## UNIVERSITÀ DEGLI STUDI DI MILANO

Scuola di Dottorato in Fisica, Astrofisica e Fisica Applicata Dipartimento di Fisica

Corso di Dottorato in Fisica, Astrofisica e Fisica Applicata Ciclo XXX

# A 4D real-time tracking device for the LHCb Upgrade II

Settore Scientifico Disciplinare  $\mathrm{FIS}/01$

Supervisore: Prof. Nicola NERI

Coordinatore: Prof. Francesco RAGUSA

Tesi di Dottorato di: Marco PETRUZZO

Anno Accademico 2018/2019

#### Commission of the final examination:

External Referees:

Prof. Luciano RISTORI, FNAL, Chicago. Dr. Massimiliano FERRO-LUZZI, CERN, Geneva.

External Members:

Prof. Tim GERSHON, University of Warwick.Prof. Angelo CARBONE, Università degli Studi di Bologna.Prof. Gianluca CAVOTO, Università degli Studi di Roma "La Sapienza".

#### Final examination:

May, 23 2019. Dipartimento di Fisica, Università degli Studi di Milano, Via Celoria 16, Milano.

#### **MIUR subjects:**

FIS/01

PACS:

$\begin{array}{c} 07.05.\mathrm{Hd} \\ 29.40.\mathrm{Gx} \end{array}$

To my family.

## Contents

| Li | st of                                                        | Figures                                                               | vii  |

|----|--------------------------------------------------------------|-----------------------------------------------------------------------|------|

| Li | st of                                                        | Tables                                                                | xi   |

| In | Introduction                                                 |                                                                       |      |

|    | Gen                                                          | eral introduction                                                     | xiii |

|    | The                                                          | sis overview                                                          | xiv  |

| 1  | LHCb detector and upgrades                                   |                                                                       | 1    |

|    | 1.1                                                          | The Large Hadron Collider at CERN                                     | 1    |

|    | 1.2                                                          | High Luminosity phase of LHC                                          | 3    |

|    | 1.3                                                          | The LHCb detector                                                     | 6    |

|    | 1.4                                                          | LHCb Upgrade I                                                        | 9    |

|    | 1.5                                                          | LHCb Upgrade II                                                       | 11   |

| 2  | Fast track finding device for efficient triggering           |                                                                       | 15   |

|    | 2.1                                                          | Challenge of event reconstruction at the High Luminosity LHC          | 15   |

|    | 2.2                                                          | Examples of fast track finding devices                                | 16   |

| 3  | Artificial retina algorithm for 2D fast track reconstruction |                                                                       | 29   |

|    | 3.1                                                          | Artificial retina algorithm                                           | 29   |

|    | 3.2                                                          | Artificial retina architecture                                        | 32   |

|    | 3.3                                                          | Tracking system prototype                                             | 35   |

| 4  | 4D real-time tracking algorithm                              |                                                                       | 43   |

|    | 4.1                                                          | Algorithm description                                                 | 43   |

|    | 4.2                                                          | Simulated response of the 4D tracking algorithm                       | 48   |

| 5  | Device architecture and implementation in FPGA               |                                                                       | 55   |

|    | 5.1                                                          | Description of the implemented modules                                | 56   |

|    | 5.2                                                          | Hold logic details, latency and throughput of the implemented modules | 81   |

|    | 5.3                                                          | Overview of the complete architecture                                 | 92   |

| 6                    | Results on a prototype device                                        |                                                          | 95  |

|----------------------|----------------------------------------------------------------------|----------------------------------------------------------|-----|

|                      | 6.1                                                                  | gFEX prototype v2 board                                  | 95  |

|                      | 6.2                                                                  | Test of optical MGT links                                | 98  |

|                      | 6.3                                                                  | Implementation of user data communication over MGT links | 100 |

|                      | 6.4 Implementation and test of the Stub Switch and Engines           | 102                                                      |     |

| 7                    | Possible application of real-time tracking algorithm to the Beam Gas |                                                          |     |

|                      | Vertex Detector                                                      |                                                          | 107 |

|                      | 7.1                                                                  | Beam Gas Vertex Detector                                 | 107 |

|                      | 7.2                                                                  | Proposed real-time reconstruction algorithm in FPGA      | 108 |

| Su                   | ımma                                                                 | ary                                                      | 121 |

| Bibliography         |                                                                      |                                                          | 123 |

| List of Publications |                                                                      |                                                          | 127 |

## List of Figures

| 1.1  | Scheme of the CERN accelerator complex                                     | 2  |

|------|----------------------------------------------------------------------------|----|

| 1.2  | LHC luminosity plan from 2010 to 2038.                                     | 5  |

| 1.3  | LHCb luminosity plan from 2010 to 2037.                                    | 5  |

| 1.4  | LHCb detector lateral view.                                                | 6  |

| 1.5  | $b\bar{b}$ production angles distribution                                  | 7  |

| 1.6  | LHCb Upgrade I detector lateral view.                                      | 10 |

| 1.7  | Tracking performance of the VELO Upgrade-I sub-detector at Upgrade I       |    |

|      | and Upgrade II conditions.                                                 | 12 |

| 1.8  | Distribution of tracks in space and time originated from different PVs.    | 13 |

| 2.1  | Pattern matching example                                                   | 17 |

| 2.2  | CDF detector scheme                                                        | 18 |

| 2.3  | SVXII sub-detector scheme                                                  | 20 |

| 2.4  | ATLAS detector scheme                                                      | 21 |

| 2.5  | ATLAS Inner Detector tracker scheme                                        | 21 |

| 2.6  | Scheme of FTK variable resolution patterns                                 | 23 |

| 2.7  | CMS detector scheme                                                        | 24 |

| 2.8  | CMS Phase II tracking system scheme                                        | 26 |

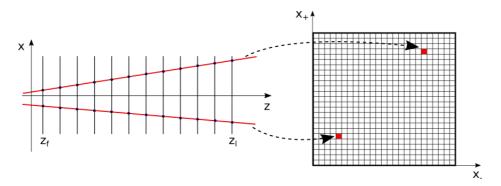

| 3.1  | 2D detector layout and visual representation of the grid of cellular units | 30 |

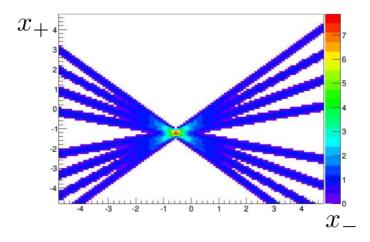

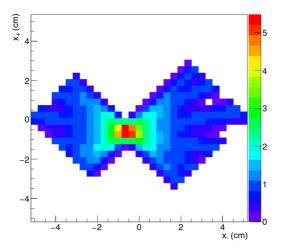

| 3.2  | Typical response of the 2D artificial retina                               | 31 |

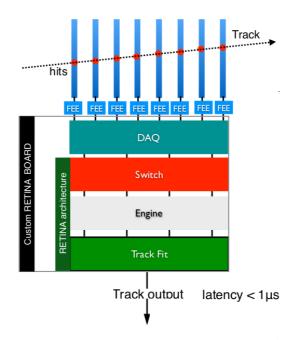

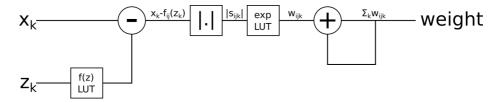

| 3.3  | Generic scheme of the artificial retina architecture                       | 32 |

| 3.4  | 2x2 Sorter scheme                                                          | 33 |

| 3.5  | Artificial retina Engine scheme                                            | 34 |

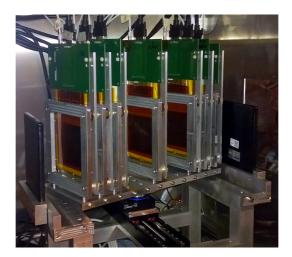

| 3.6  | Silicon telescope sensor module                                            | 36 |

| 3.7  | Silicon strip telescope at SPS                                             | 36 |

| 3.8  | MAMBA DAQ board                                                            | 37 |

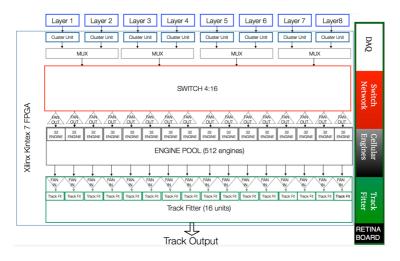

| 3.9  | Hardware specific scheme of the artificial retina architecture             | 38 |

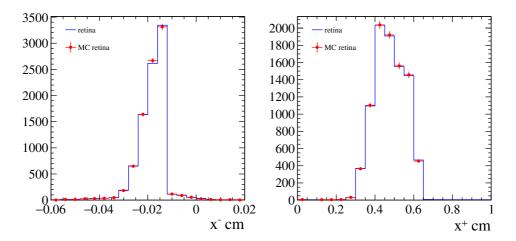

| 3.10 | 2D artificial retina response at testbeam                                  | 40 |

| 3.11 | Artificial retina track parameters distribution                            | 40 |

| 3.12                                      | Residuals distribution for the artificial retina                                                                                            | 41  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

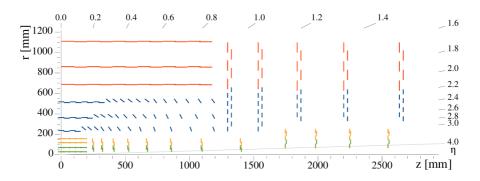

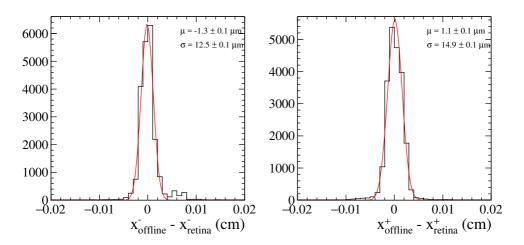

| 4.1                                       | Layout of a VELO-like detector and visual representation of the grid of cellular units                                                      | 46  |

| 4.2                                       | Typical response of the 4D tracking algorithm cellular units                                                                                | 47  |

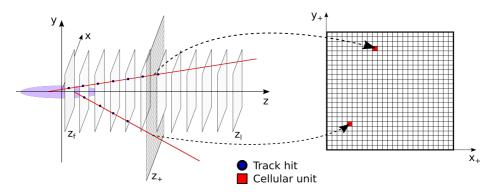

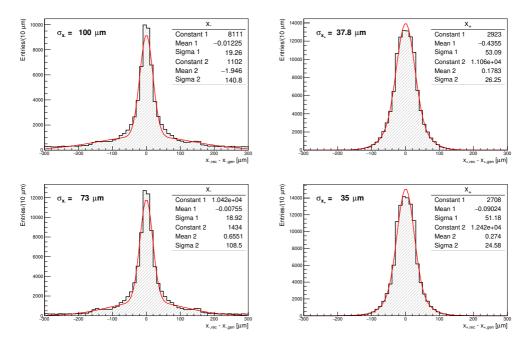

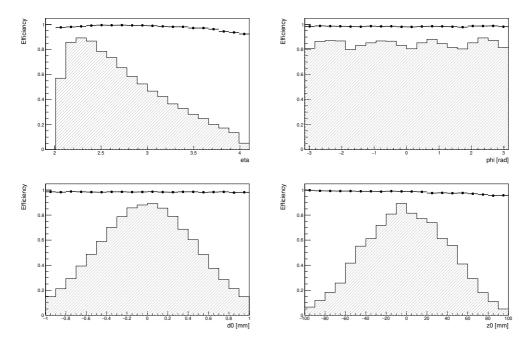

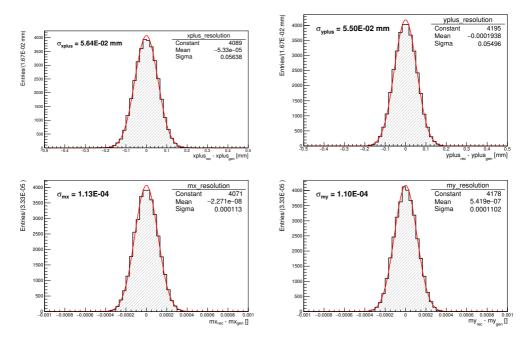

| 4.3                                       | Residual distribution of spatial track parameters from high level simulation                                                                | 50  |

| 4.4                                       | Residual distribution of time track parameters from high level simulation                                                                   | 51  |

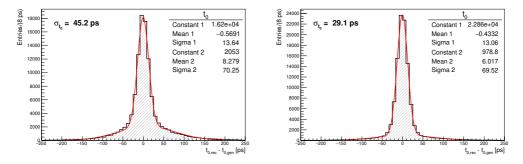

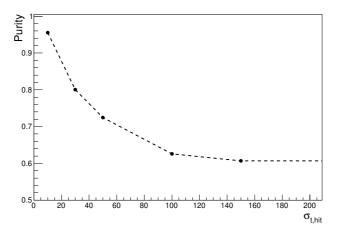

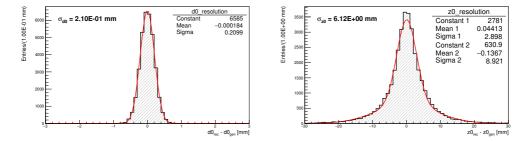

| 4.5                                       | Track reconstruction purity from high level simulation                                                                                      | 52  |

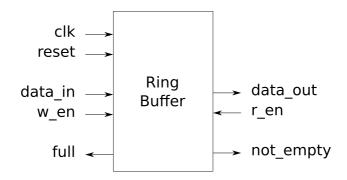

| 5.1                                       | Ring Buffer port scheme                                                                                                                     | 59  |

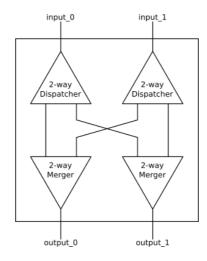

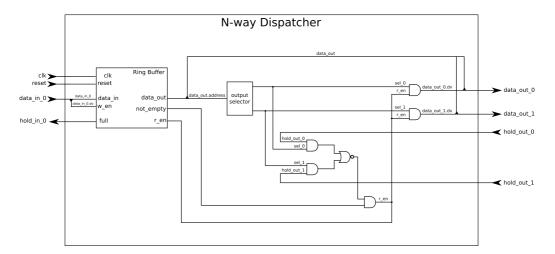

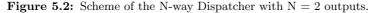

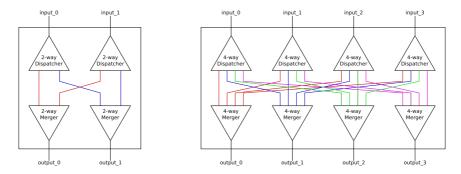

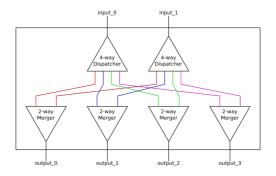

| 5.2                                       | N-way Dispatcher scheme                                                                                                                     | 62  |

| 5.3                                       | N-way Merger scheme                                                                                                                         | 66  |

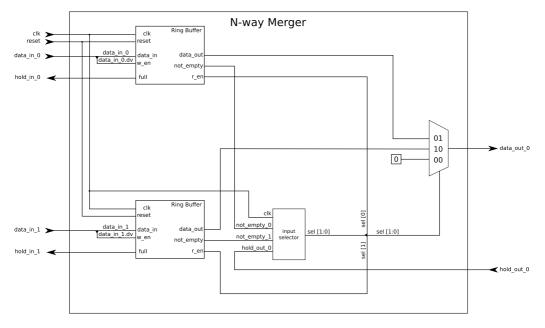

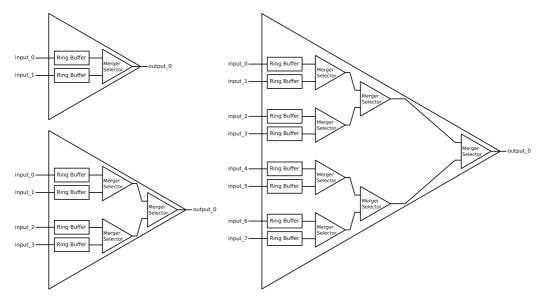

| 5.4                                       | Structure of the N-way merger                                                                                                               | 67  |

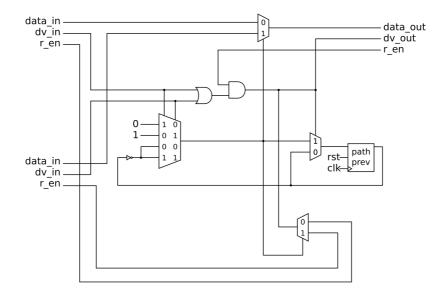

| 5.5                                       | Merger Selector logic                                                                                                                       | 68  |

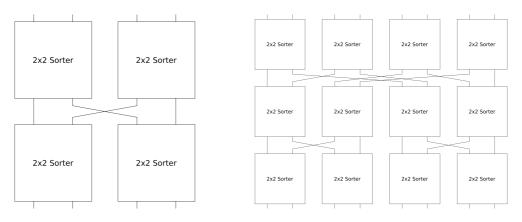

| 5.6                                       | NxN Sorter structure                                                                                                                        | 70  |

| 5.7                                       | Non-square Sorter structure                                                                                                                 | 70  |

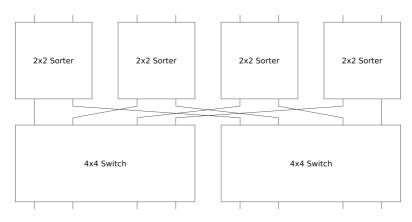

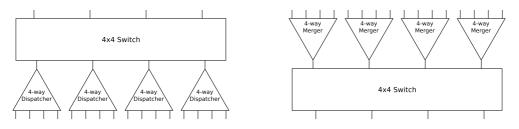

| 5.8                                       | NxN Switch structure                                                                                                                        | 72  |

| 5.9                                       | NxN Switch recursive structure                                                                                                              | 72  |

| 5.10                                      | Non-square Switch structure                                                                                                                 | 73  |

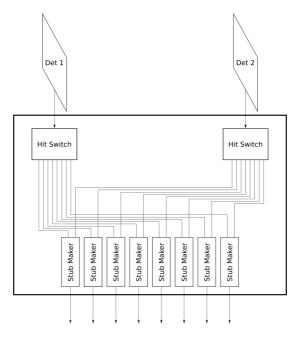

| 5.11                                      | Stub Maker logic                                                                                                                            | 75  |

| 5.12                                      | Scheme of the Stub Constructor                                                                                                              | 78  |

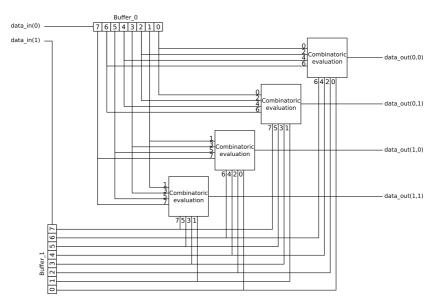

| 5.13                                      | Engine logic                                                                                                                                | 80  |

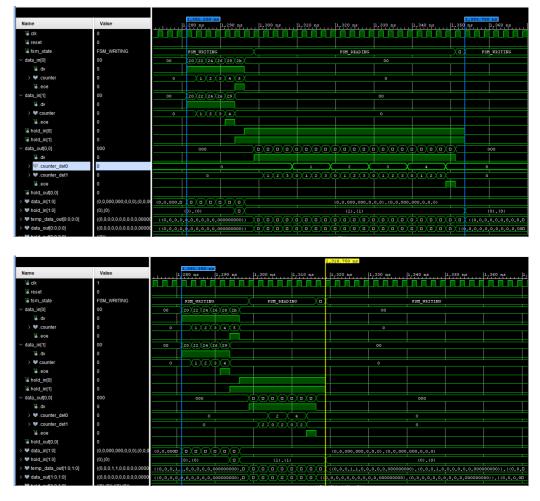

| 5.14                                      | Ring Buffer logic testbench                                                                                                                 | 83  |

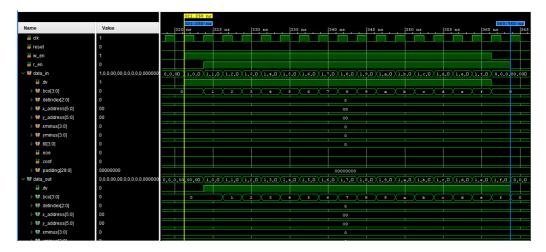

| 5.15                                      | N-way Dispatcher logic testbench                                                                                                            | 85  |

| 5.16                                      | N-way Merger logic testbench                                                                                                                | 88  |

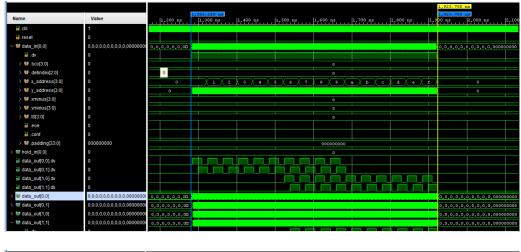

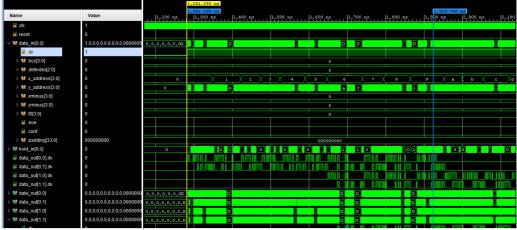

| 5.17                                      | Stub Maker logic testbench                                                                                                                  | 91  |

| 5.18                                      | Engine logic testbench                                                                                                                      | 92  |

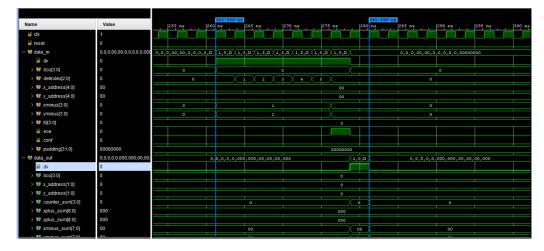

| 5.19                                      | Architecture of the 4D real-time tracking system                                                                                            | 93  |

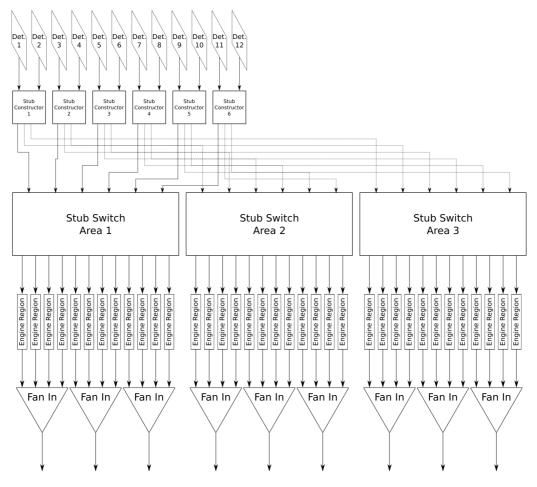

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Picture and floor plan of the fully assembled gFEX prototype v2 board<br>Xilinx Virtex UltraScale XCVU095 and XCVU160 product table compar- | 96  |

| 0.2                                       | ison                                                                                                                                        | 97  |

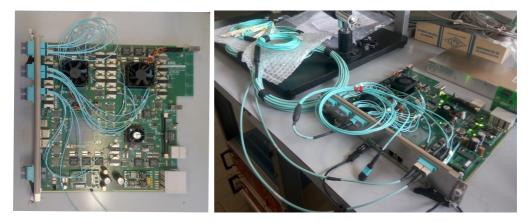

| 6.3                                       | Picture of the gFEX prototype v2 board at INFN - Milano                                                                                     | 98  |

| 6.4                                       | gFEX board test setup                                                                                                                       | 99  |

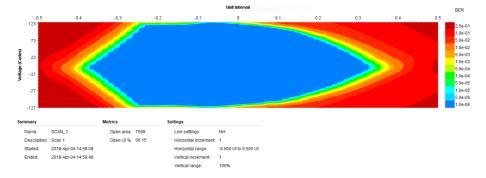

| 6.5                                       | Eye diagram example for one MGT link under test.                                                                                            | 100 |

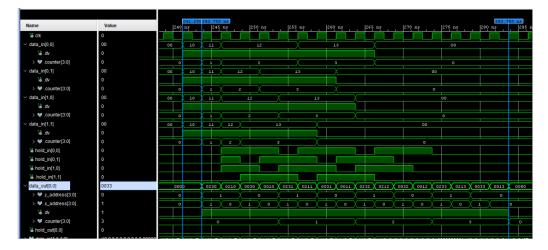

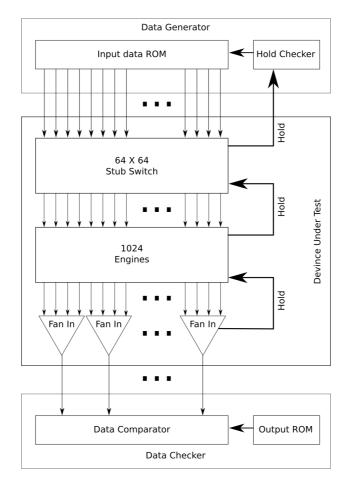

| 6.6                                       | Architecture test for 4D real-time tracking algorithm sub-system                                                                            | 104 |

|                                           |                                                                                                                                             |     |

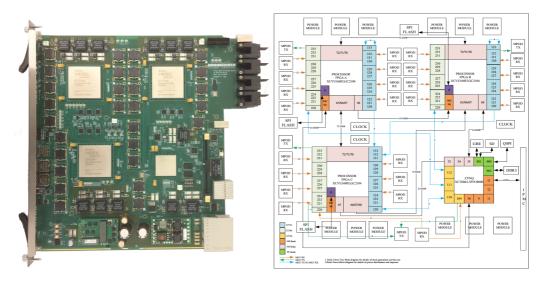

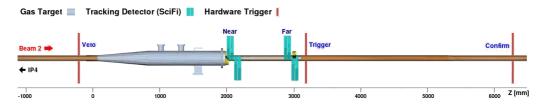

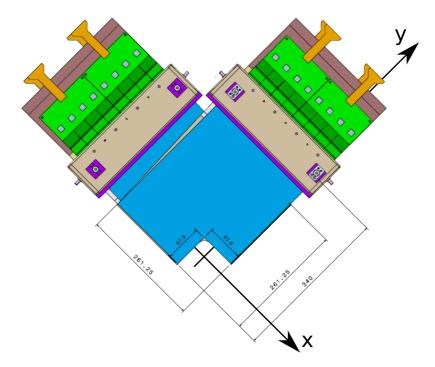

| 7.1                                       | BGV layout                                                                                                                                  | 107 |

| 7.2                                       | BGV sensors arrangement                                                                                                                     | 109 |

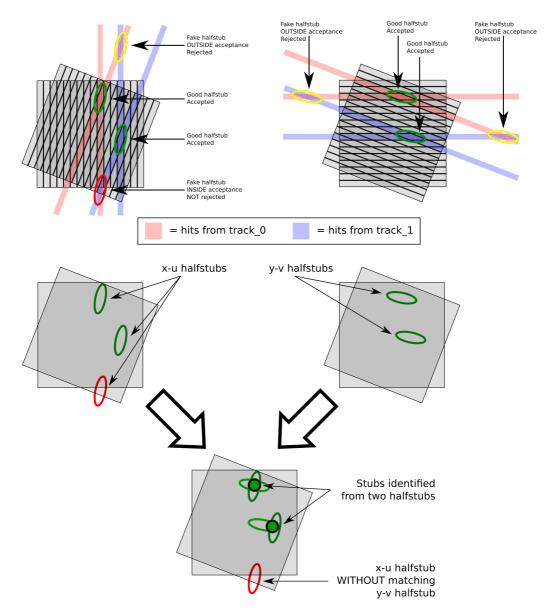

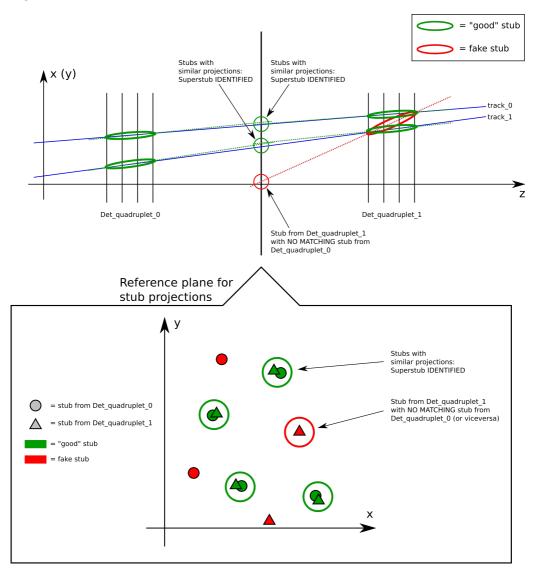

| 7.3                                       | Example of identification of halfstubs and stubs in the BGV                                                                                 | 111 |

| 7.4                                       | Example of identification of superstubs in the BGV                                                                                          | 112 |

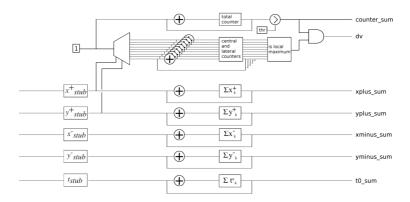

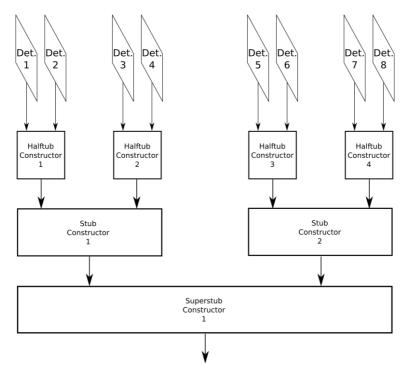

| 7.5                                       | BGV reconstruction algorithm algorithm architecture.                                                                                        | 113 |

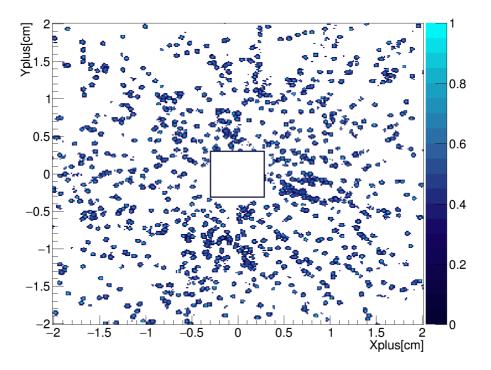

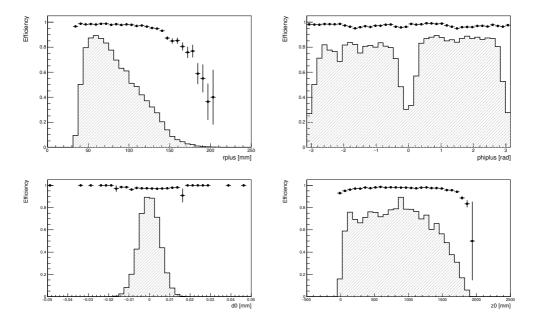

| 7.6                                       | BGV resolutions on $(x_+, y_+, m_x, m_y)$ track parameters from simulated events                                                            |     |

|                                           |                                                                                                                                             | 115 |

| 7.7                                       | BGV resolutions on $(d_0, z_0)$ track parameters from simulated events.                                                                     | 116 |

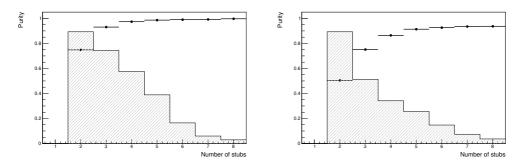

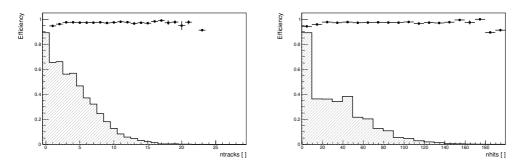

| 7.8  | BGV reconstruction efficiency vs. $r_+, \phi_+, d_0, z_0$ .  | 116 |

|------|--------------------------------------------------------------|-----|

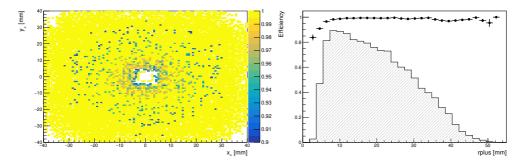

| 7.9  | BGV reconstruction efficiency vs. number of tracks and hits. | 117 |

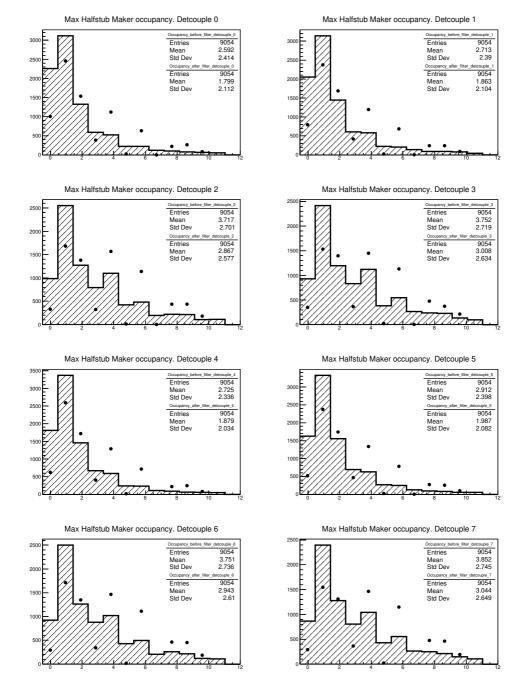

| 7.10 | BGV Halfstub Makers occupancy                                | 118 |

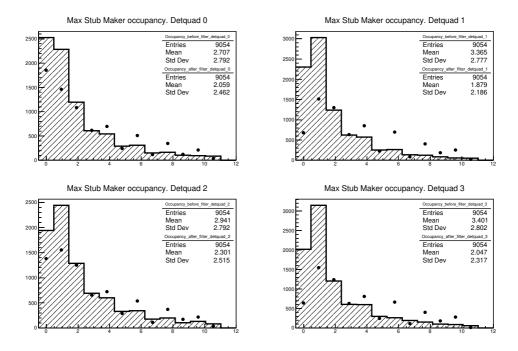

| 7.11 | BGV Stub Makers occupancy                                    | 119 |

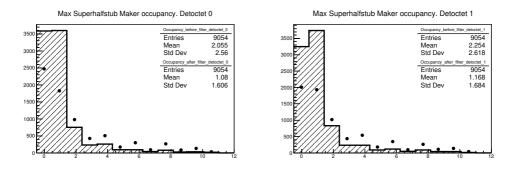

| 7.12 | BGV Superstub Makers occupancy                               | 120 |

## List of Tables

| 3.1 | Artificial retina latency and FPGA resources                                                 | 39       |

|-----|----------------------------------------------------------------------------------------------|----------|

|     | Sensors positions of the VELO-like simulated tracker detector<br>Track parameters resolution | 48<br>51 |

| 7.1 | Longitudinal positions of the BGV sensors                                                    | 110      |

## General introduction

I started my Ph.D. at the Physics Department of Università degli Studi di Milano, in association with the Istituto Nazionale di Fisica Nucleare - Sezione di Milano, in March 2015. My research activity as Ph.D. student has been carried within the LHCb collaboration and the INFN CSN5 RETINA and TIMESPOT projects.

My contribution to the LHCb collaboration was focused on the testbeam campaign for the study and characterization of the silicon sensors for the Upgrade I of the Upstream Tracker sub-detector of the LHCb experiment. I participated to different testbeam campaigns at the CERN Super Proton Synchrotron (SPS) in 2014, 2015, 2016; I mainly worked on a custom DAQ board based on Field Programmable Gate Array (FPGA) technology for the readout of the silicon sensors that has been developed at INFN-Milano. I also took part in the data taking shifts and in the analysis of the testbeam data; during the last experience I co-directed the testbeam activity during the preparation, the set-up of the experimental system and the data taking period. Within the RETINA project I worked on the design of a device for real-time tracking of charged particles in FPGA; in particular I developed a C++ software simulation and the VHDL firmware implementation of the system in FPGA. A prototype, based on a single-sided telescope, has been successfully tested at SPS in October 2015.

The main result of my Ph.D. research activity, documented in this thesis, has been the development and implementation of a new algorithm for application to a 4D (space-time) tracking system to reconstruct the particle trajectories in real-time. The application of such a system to the Upgrade II of the LHCb experiment has been considered in this work; an application to the Beam Gas Vertex Detector has also been considered. The inclusion of the time information in the first stages of the trigger decision would help in mitigating the effects of the pile-up in the upgraded conditions of the LHC collider, allowing LHCb to exploit the larger data sample for its physics program. The proposed tracking devices at high rates with latency below 1  $\mu$ s. The performances of the 4D fast tracking device and its firmware implementation have been tested on a custom board equipped with latest generation FPGA (Xilinx Virtex UltraScale, *XCVU095*) and high-speed serial links to sustain up to 1.6 Tbps input data bandwidth. The response of the LHCb VELO detector based on pixel sensors has been simulated assuming 30 ps time resolution. Simulated data from a sector (~ 1/64) of the detector have been provided to

the fast track finder prototype to test the system. This demonstrator prototype has to be considered as a building block of a large scale system capable to process a large tracking detector of a LHC experiment.

#### Thesis overview

My Ph.D. thesis is inserted in the context of the Upgrade II of the LHCb experiment, for the High Luminosity phase of LHC. In particular the thesis is focused on the development of a hardware demonstrator of a fast track finder using precise space and time information of the particle hits in the detector, *i.e.* a possible upgraded VELO detector of the LHCb experiment, able to identify and reconstruct the particle tracks in real time with low latency. This feature would allow to use the track information in the early stage of the trigger decision chain.

In the past the Silicon Vertex (SVT) of the CDF experiment at Fermilab played a very important role in the study of heavy flavour physics thanks to the possibility of fast track reconstruction with a very good quality. The selection was based on the track impact parameter and the identification of displaced vertices with respect to the position of the primary interaction. The SVT worked as part of the Level 2 of a three-level trigger system, and implemented a highly parallelized pattern-matching using a custom-made processor, the associative memory (AM). In particular the AM compares in parallel the hits from the tracking system to several precomputed patterns, providing the tracks candidates to be fitted using a simplified fitting algorithm in fast FPGAs. This made possible to reconstruct tracks with offline-like resolution and latency of about 20  $\mu$ s allowing the Level 2 trigger to match the full output rate of approximately 30 KHz of the Level 1. The evolution of this concept is exploited by ATLAS in the *Fast TracKer* (FTK) device, that is being commissioned and will provide the information of the already reconstructed tracks to the High Level Trigger (HLT). The working principle is substantially unchanged while the modern electronics and a strongly pipelined architecture allow to handle a much larger number of patterns and process the more complex ATLAS events at 100 KHz rate, with an average latency below 100  $\mu$ s.

The LHCb experiment is going to run at an instantaneous luminosity of  $2 \times 10^{33}$  cm<sup>-2</sup>s<sup>-1</sup> during the Run 3, from 2021 to 2023, and the collaboration is currently working on an extensive upgrade of the detector and the DAQ system in order to strengthen the physics program. In particular the tracking detectors will be completely replaced with a pixel Vertex Locator (VELO), a silicon tracking station before the magnet, the Upstream Tracker (UT), and a Scintillating Fibre downstream tracker (SciFi). The detector will be read out at 40 MHz and a full software trigger will process the full rate of inelastic collisions delivered by the LHC, providing significantly increased efficiency in hadronic final states. After the Long Shutdown 3 (LS3) the LHC conditions will be upgraded to the so-called High Luminosity phase (HL-LHC) and the luminosity at the LHCb interaction point during the Run 4, expected from 2026 to 2030, will be levelled to the same conditions of the Run 3, allowing the Upgrade I detector to continue operating without major modifications. At the end of the Run 4 the precision on some important measurements will still be limited by statistics and many parts of the detector will need to be replaced due to

the radiation damage. For these reasons the LHCb collaboration has already proposed an Upgrade II, which will operate at a luminosity of around  $1 - 2 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, to exploit the potential of the HL-LHC during the Run 5, expected to start in 2031.

The trigger requirements at LHCb are very challenging due to the need of reading out the whole detector at 40 MHz and processing the full event information, since the current first level hardware trigger would be limited at higher luminosities for hadronic channels. During Run 2 it was demonstrated that a full software reconstruction is possible for realtime calibration and alignment and the strategy for the software and the computing of the Upgrade I are under review. The software framework is going to be revised to full profit of modern multi-core architectures, while solutions based on GPUs and hardware accelerators are under study. The operation of the LHCb Upgrade II will provide even more significant challenges; in fact the increased luminosity will lead to a higher event complexity and higher data volumes to process, affecting the output bandwidth to be managed by the trigger and offline system that will have to be improved to cope with the harsher environment. Even though the Upgrade II trigger will remain software based, it is not clear if the Upgrade I solutions can be adopted, even considering the expected computing power growth during the 2020s. For this reason the use of dedicated processors has to be considered as a viable solution to solve specific tasks and evaluate relevant information to be fed to the reconstruction software at the earliest trigger level. An example of these tasks could be the early reconstruction of the tracks downstream of the magnet; in fact, these are not included in the baseline trigger scheme due to the CPU time required to execute the search. Another example is the identification and reconstruction of tracks in the VELO sub-detector, and eventually in the UT; this task is computationally intensive and the use of custom processor would free a significant amount of CPU computing power. Along with pure algorithm and computing strategies, another relevant help could come by the inclusion of timing information of the hits, currently not available, that would help in suppressing the combinatoric background, reducing the negative effects of the pile-up as the incorrect track-vertex association.

#### Organizational note

The present thesis is organized as follows:

- Chapter 1. The LHC collider and in particular the LHCb experiment and the Upgrade I and Upgrade II are described.

- Chapter 2. An overview of the existing fast tracking devices, along with their use inside the trigger chain, is given.

- Chapter 3. The artificial retina for fast track reconstruction is described: the algorithm, the hardware implementation on a hardware prototype and the testbeam results are discussed.

- Chapter 4. An algorithm for real-time 4D track reconstruction using precise space and time information of the detector hits is presented, together with the results from the simulated response of the tracking device.

- Chapter 5. The architecture of the hardware implementation in FPGA is described.

- Chapter 6. The results from tests of the algorithm implemented on a prototype board and fed with data from a sector of the VELO sub-detector of the LHCb experiment are reported.

- Chapter 7. A possible application of a real-time tracking algorithm in FPGA is proposed for the LHC Beam Gas Vertex detector.

## LHCb detector and upgrades

The LHCb experiment [1] is one of the four main experiments located at the Large Hadron Collider (LHC) [2] at CERN.

In this chapter we will provide an overview of the LHCb experiment and its upgrades within the context of the LHC upgrade schedule to the High Luminosity phase (HL-LHC) [3], planned to begin after the Long Shutdown 3 (LS3, 2024-2026); in particular, the High Luminosity phase for LHCb will begin after the Long Shutdown 4 (LS4, 2030).

### 1.1 The Large Hadron Collider at CERN

The Large Hadron Collider is the world's largest and most powerful particle accelerator, located at CERN. The LHC is a two-ring superconducting accelerator, measuring 26.7 km in circumference. It is installed 100 m underground at the Franco-Swiss border near Geneva, in the tunnel that previously hosted the *Large Electron Positron* (LEP) collider which operated from 1989 to 2000.

The LHC is able to accelerate two counter-rotating beams of both protons and ions. The first case represents the main operation mode of the LHC experiments, investigating in particular proton-proton (pp) collisions at the center-of-mass energy of  $\sqrt{s} = 13$  TeV, near the maximum design value of 14 TeV.

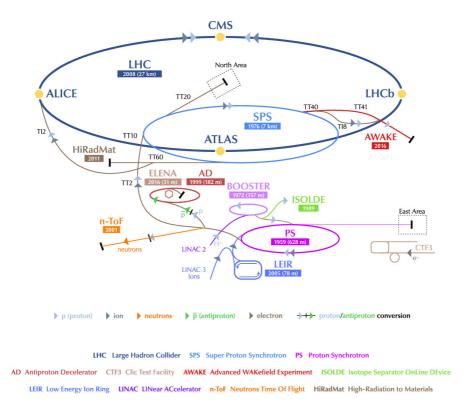

The LHC accelerator ring represents the last acceleration stage, after several particle accelerators. The scheme of the CERN accelerator complex, with the positions of the four LHC experiments highlighted along the LHC ring, is shown in Fig. 1.1.

At the beginning, protons are obtained by ionizing hydrogen gas with an electric discharge and are accelerated by the LINAC2 (*Linear Accelerator 2*) up to 50 MeV. The protons are then injected into the PSB (*Proton Synchrotron Booster*) in which the proton beam energy is increased up to 1.4 GeV. The PS (*Proton Synchrotron*) machine accelerates protons up to 26 GeV and the beam is injected into the SPS (*Super Proton Synchrotron*) accelerator where the proton beam reaches the energy of 450 GeV. The SPS represents the last pre-acceleration stage before the LHC: the beam is split and injected into the LHC where two separate beams travel in clockwise and anticlockwise directions and are accelerated up to 6.5 TeV. After all the acceleration stages have been performed the two beams collide in four interaction points where the main LHC experiments are located: ALICE [4], ATLAS [5], CMS [6], LHCb [1]. Each beam consists nominally of 2808 proton

Figure 1.1: Scheme of the CERN accelerator complex showing the acceleration facilities and the four main experiments.

bunches spaced by 25 ns, resulting in the expected bunch crossing frequency of 40 MHz. Each bunch is about 7.5 cm long in the beam direction and nominally contains  $1.15 \times 10^{11}$  protons leading to the instantaneous luminosity of  $2 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, reached during year 2018 at ATLAS and CMS interaction points, which is a factor of two higher than the LHC design luminosity  $(1 \times 10^{34} \text{ cm}^{-2}\text{s}^{-1})$ . At the LHCb interaction point the instantaneous luminosity is reduced to  $5 \times 10^{32} \text{ cm}^{-2}\text{s}^{-1}$  using a larger transverse beam size in order to reduce the number of interactions per bunch crossing; this is essential in terms of data quality and detector radiation damage. At the ALICE interaction point the luminosity (for *pp* interactions) is further reduced to  $4 \times 10^{30} \text{ cm}^{-2}\text{s}^{-1}$ .

The main four LHC experiments are designed for different scientific programs:

• The ATLAS (*A Toroidal LHC Apparatus*) and CMS (*Compact Muon Solenoid*) experiments are General Purpose Detectors (GPDs) and are designed to study collisions producing high transverse momentum particles. Their physics program is focused on the study of the Higgs Boson properties and also includes search for direct signals of New Physics beyond the Standard Model, search of Dark Matter candidates and Standard Model precision measurements. Besides sharing similar scientific goals, the ATLAS and CMS experiments differ in the apparatus design

whose main difference can be identified in the magnet systems, while both are based on a cylindrical *barrel* geometry and two symmetrical *end caps* placed along the direction of the beam axis.

- ALICE (*A Large Ion Collider Experiment*) mainly profits of heavy ions collisions, in particular lead ions, and it is designed to investigate the strong interaction theory through the study of Quark-Gluon Plasma state. The detector uses both a Time Projecting Chamber and a forward spectrometer.

- The LHCb (*LHC beauty*) is a single-arm forward spectrometer experiment. It is dedicated to the indirect search of New Physics beyond the Standard Model, via precise measurement of the *CP* violation and rare decays of bottom and charm hadrons, using the vast statistics of heavy flavour hadrons produced in proton-proton (pp) collisions in the forward region. Further details will be provided in the following sections.

In addition to these four experiments, three smaller experiments dedicated to forward physics are present at LHC.

- TOTEM [7] (**TOT**al Elastic and diffractive cross section Measurement), located at the CMS interaction point, studies the total proton-proton cross-section, elastic scattering and diffractive dissociation.

- LHCf [8] (*LHC forward*), located at the ATLAS interaction point, is used for engineering measurements for astroparticle experiments simulating cosmic rays in laboratory conditions.

- MoEDAL [9] (*Monopole and Exotics Detector At the LHC*), located at the LHCb interaction point, is dedicated to the search of the magnetic monopoles.

## 1.2 High Luminosity phase of LHC

The LHC was successfully commissioned in 2010 and started delivering proton-proton collisions at a centre-of-mass energy of  $\sqrt{s} = 7$  TeV in 2010-2012, and at  $\sqrt{s} = 8$  TeV from April 2012 until the end of the Run 1.

The Run 2 of LHC started in June 2015 and ended in December 2018. During this period the centre-of-mass energy of pp collision has reached the value of  $\sqrt{s} = 13$  TeV and an instantaneous luminosity of  $2 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, representing twice the nominal design value, was achieved. At the end of the Run 2, the ATLAS experiment collected a total integrated luminosity of 187.1 fb<sup>-1</sup>, the CMS experiment 192.0 fb<sup>-1</sup>, the LHCb experiment 10.1 fb<sup>-1</sup> and the ALICE experiment 81.7 pb<sup>-1</sup>, considering the proton and ion delivered luminosities<sup>1</sup>.

During the LS2 the 160 MeV LINAC4 accelerator will be connected to the PSB while all the pre-accelerators and infrastructures will undergo major maintenance and consolidation.

<sup>&</sup>lt;sup>1</sup>http://acc-stats.web.cern.ch/acc-stats/#lhc/.

During the Run 3 of LHC, expected to start in 2021, the centre-of-mass energy for pp collisions is expected to be increased up to  $\sqrt{s} = 14$  TeV and the instantaneous luminosity is expected to stay at the late 2018 value, reaching a delivered integrated luminosity of  $400 \text{ fb}^{-1}$  by the end of the run. In particular during the Run 3 the statistical gain in running the accelerator without a luminosity increase will become marginal and if on one hand this would lead to doubling the statistics from the Run 2 to the Run 3, on the other hand the time necessary to reduce by half the statistical errors in measurement results would be ten years starting from the end of Run 2 [10]. For this reason and to fully exploit the potential of the LHC a major upgrade of the accelerator has been approved. The so-called *High Luminosity LHC* (HL-LHC) [11] will operate after the LS3 and will increase the luminosity by a factor five with respect to the current nominal design value of  $10^{34} \text{ cm}^{-2}\text{s}^{-1}$ .

The LS3 is scheduled to start in 2024 and will last 18 months. During the shutdown the LHC will undergo a major upgrade of its components, like low- $\beta$  quadrupole triplets and the use of crab cavities at the interaction regions, in preparation for the HL-LHC. Moreover at that time many critical components of the accelerator will have reached the end of their lifetime and the upgrade is necessary to allow the collider to work beyond 2025.

With the Run 4 of LHC, from 2026 to 2029, the High Luminosity phase will start, making the machine able to deliver a peak luminosity of  $7.5 \times 10^{34}$  cm<sup>-2</sup> without beam levelling, allowing an integrated luminosity of 300 - 350 fb<sup>-1</sup> per year, for an expected total integrated luminosity of 4000 fb<sup>-1</sup> after twelve years of operation, in 2037, that corresponds to about ten times the integrated luminosity expected to be obtained at the end of the Run 3. In particular, these value are intended to be valid for ATLAS and CMS experiments that operate at the same level of luminosity delivered by the accelerator.

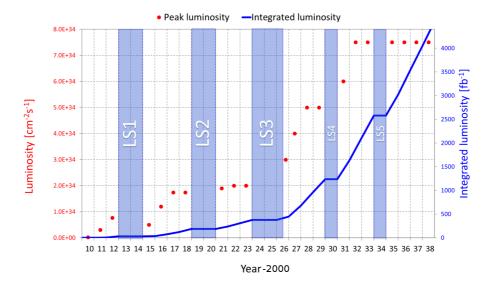

The LHC luminosity plan from 2010 to 2038 is shown in Fig. 1.2. The instantaneous and integrated luminosity are represented by red dots and solid blue line, respectively.

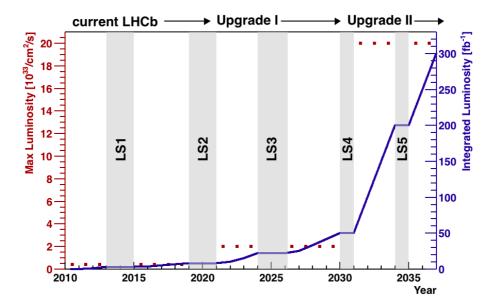

In the case of the LHCb experiment the instantaneous luminosity will not be increased after the Run 3 but only after the LS4, and the High Luminosity phase of LHCb will start with the beginning of the Run 5. By the end of 2037 an integrated luminosity of  $300 \text{ fb}^{-1}$  is expected, to be compared with the value of  $50 \text{ fb}^{-1}$  expected at the end of the Run 4.

The luminosity plan from 2010 to 2037 for the LHCb experiment is shown in Fig. 1.3. The LHCb experiment makes use of the beam levelling to reduce the instantaneous luminosity below the values delivered by the LHC accelerator. The instantaneous and integrated luminosity are represented by red dots and solid blue line, respectively.

The HL-LHC will rely on a number of key innovations that push accelerator technology beyond its present limits. Among these are cutting-edge 11-12 tesla superconducting magnets, compact superconducting cavities for beam rotation with ultra-precise phase control, new technology and physical processes for beam collimation and 100 metre-long high-power superconducting links with negligible energy dissipation. Details on the HL-LHC project can be found in Ref. [3].

Figure 1.2: LHC luminosity plan from 2010 to 2038. The red dots represent the value of measured or predicted instantaneous luminosity. The solid blue line represents the value of measured or predicted integrated luminosity (for the ATLAS and CMS experiments).

Figure 1.3: Luminosity plan from 2010 to 2037 for the LHCb experiment. Red dots represent the value of measured or predicted instantaneous luminosity. Solid blue line represents the value of measured or predicted integrated luminosity.

## 1.3 The LHCb detector

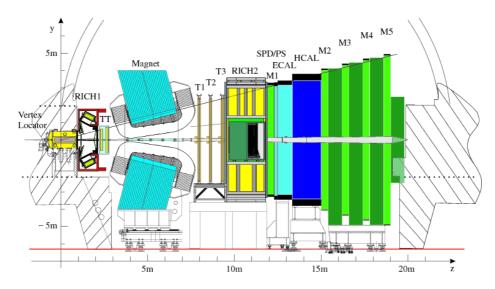

The LHCb detector is a single-arm forward magnetic spectrometer with a polar angle coverage from 15 mrad to 300 (250) mrad in the horizontal (vertical) plane, corresponding to a pseudorapidity  $(\eta)$  range of  $2 < \eta < 5$  in the forward direction.

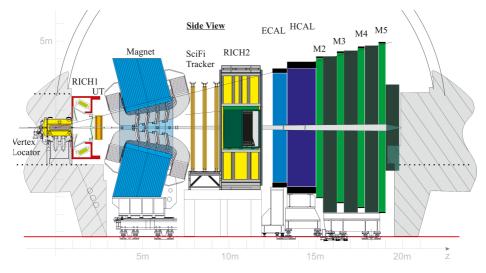

The layout of the LHCb detector and its sub-detectors is shown in Fig. 1.4. The beams travel along the direction of the z-axis and collide in the region centred around the axes origin, while the magnetic field is oriented along the vertical direction. The coordinate system of the LHCb experiment is described in Ref. [12] and can be summarized as follows:

- the origin of the coordinate system is the interaction point;

- the *x*-axis is horizontal, and points from the interaction point towards the outside of the LHC ring;

- the *y*-axis is perpendicular to the *x*-axis and to the beam line pointing upwards and is inclined by 3.601mrad with respect to the vertical;

- the z-axis points from the interaction point towards the LHCb detector and is aligned with the beam direction, to create a right handed Cartesian coordinate system x-y-z.

Figure 1.4: Lateral view of the LHCb detector. The interaction region is centred around the axes origin.

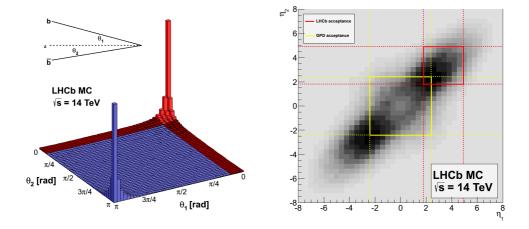

The peculiar geometry of the LHCb detector, compared to the typical design of the general purpose detectors at CERN, is motivated by the fact that in proton-proton collisions at the LHC energy scale the  $b\bar{b}$  hadron pairs are mainly produced at small polar angles with respect to the beam direction as shown in Fig. 1.5 [13], both in the forward and backward direction, with relatively high momentum. Although the geometrical coverage of the detector corresponds only to 4% of the total solid angle, for a centre-of-mass energy

of  $\sqrt{s} = 14$  TeV the probability to find either the *b* or the  $\bar{b}$  hadron within the detector acceptance amounts to 27%, while the probability of finding the  $b\bar{b}$  pair is 24%.

**Figure 1.5:** Left: Distribution of the production polar angles of the *b* quark and  $\bar{b}$  antiquark in  $b\bar{b}$  quark-pair production processes. Right: Same distribution as a function of the pseudorapidity of the *b* quark and  $\bar{b}$  antiquark. The red square highlights the geometrical acceptance of the LHCb detector, compared to a general purpose detector, highlighted by the yellow square. Figure from Ref. [13].

#### 1.3.1 Tracking system

The tracking system of the LHCb experiment is based on several tracking sub-detectors.

- The Vertex Locator (VELO) [14] is positioned near the interaction region and it is dedicated to the precise reconstruction of primary and displaced secondary vertices. It consists of 21 disk-shaped tracking stations based on silicon strip sensors, measuring separately the radial and azimuthal coordinates of track hits in the sensors.

- The Tracker Turicensis (TT) is a tracking detector placed upstream of the magnet. It is mainly dedicated to the matching of tracks reconstructed in the VELO detector with tracks reconstructed downstream of the magnet, in order to reduce the ghost tracks. It is also dedicated to the reconstruction of tracks produced by the decay of long-lived particles. The TT consists of four layers of silicon strip sensors arranged in *axial-stereo* configuration: the silicon strips in the first and last layers are oriented along the vertical direction, the second and third sensors are tilted by  $+5^{\circ}$  and  $-5^{\circ}$ . The *axial-stereo* configuration allows to reconstruct three dimensional trajectories, with better resolution in x than in y direction.

- Three tracking stations (T1, T2, T3) are placed after the magnet; each station consists of two separate detectors based on different technologies, the Inner Tracker (IT) [15] and the Outer Tracker (OT) [16]. The IT, closer to the beam axis, is

a cross-shaped detector based on silicon strip sensors arranged in a configuration similar to that of the TT. The IT has a finer segmentation with respect to the OT but only covers the 2% of the full detector acceptance, while containing 20% of tracks produced in pp collisions. The OT is positioned around the IT to reach the full detector acceptance coverage. Each station has four layers arranged in the same configuration of each IT station. The OT is a drift gas detector based on small straw tubes aligned along the vertical direction: when a particle crosses a straw-tube, the electrons produced by the ionization of the gas drift towards the anode wire and, at the end, generate an avalanche signal which is measured. A time-to-digital converter measures the arrival time of the signal and by comparison with the LHC bunch clock it is possible to estimate the horizontal position of the hit with 200  $\mu$ m space resolution.

• The dipole magnet provides an integrated field of 4 Tm in the vertical direction that allows to estimate the charged particle momenta by measuring the track trajectory curvature in the horizontal (x-z) plane.

#### **1.3.2** Particle identification

The particle identification in the LHCb experiment is based on two ring imaging Cherenkov detectors (RICH1, RICH2) [17], a calorimeter detector [18] and five muon stations [19]. The RICH detectors are based on the emission of Cherenkov radiation and they are primarily dedicated to distinguish between kaons and pions. They identify charged particles with momenta in a range from 2 to 100 GeV/c. In particular the RICH1 sub-detector, located before the magnet, is optimized for low-momentum (< 60 GeV/c) particles and covers the full detector acceptance. The RICH2 sub-detector, located after the magnet is dedicated to high-momentum particles (> 15 GeV/c) and covers a reduced acceptance from 15 mrad to 120 (100) mrad in the horizontal (vertical) plane. The Cherenkov light emitted in the RICH detector is guided outside the LHCb acceptance using spherical and flat mirrors, then measured by a matrix of Hybrid Photon Detectors. The typical pattern of Cherenkov light is represented by cones that are detected as rings. The particle velocity is estimated from the measurement of the ring radius. This information combined with the track momentum allows to evaluate the mass of the candidate particle. The RICH1 and RICH2 sub-detectors differ in terms of radiation mediums and for the material and arrangement of the mirrors.

The calorimeter system is dedicated to identify electrons, photons and hadrons providing the measurement of their energy. The calorimeter system comprises the Electromagnetic Calorimeter (ECAL) and the Hadron Calorimeter (HCAL), both placed after the RICH2. It covers an angular acceptance range from 25 mrad to 300(250) mrad in the horizontal (vertical) plane, where the inner acceptance was driven by the particle density near the beam pipe. The ECAL is equipped with two additional sub-detectors: the Scintillating Pad Detector (SPD) and the Preshower Detector (PS).

The SPD is based on layers of scintillators. It is used to distinguish electrons from photons and pions. A 12 cm thick lead layer is inserted between the SPD and the PS. Electrons

passing the lead layer have higher probability to shower, with respect to hadrons, and are detected in the PS. In this way the PS can distinguish between electrons and hadrons. The ECAL and the HCAL are the main components of the calorimeter system. The ECAL measures the energy of particles that interact by electromagnetic processes. It consists of alternating layers of scintillating material and lead absorbers. When a particle passes through the absorber it produces a shower originated from bremsstrahlung and pair production mechanisms; the shower interacts and deposits its energy in the scintillating material, the converted photons travel to the photomultipliers where the signal is collected and recorded.

The HCAL works in a similar fashion and measures the energy of particles that interact by strong nuclear interactions. The difference with the ECAL consists in the use of iron (instead of lead) for the absorber layers.

#### 1.3.3 Muon system

The muon system is read out at 40 MHz and the presence of muons with high transverse momentum is a strong signature to perform hardware level trigger decisions (L0 trigger). The muon system consists of five muon stations (M1-M5) that cover the angular acceptance range from 20 (16) mrad to 306 (258) mrad in the horizontal (vertical) plane. The first station is placed between the RICH2 and the ECAL (SPD/PS), in order to improve the measurement of the transverse momentum for muons that are detected also in the other stations (M2-M5) placed after the HCAL. Stations from M2 to M5 are separated by 80 cm thick iron absorber layers, to select muons with different energies. In particular the minimum momentum to traverse all the layers is 6 GeV/c. Each station is divided in four quadrants, each of them is divided in four regions (R1-R4) arranged around the beam pipe whose dimensions follow the scale ratio (from R1 to R4) of 1:2:4:8 in order to have regions with similar occupancies. The inner region of the first station (M1-R1) is instrumented with triple-gas electron multiplier (triple-GEM) detectors, which better cope with the higher particle flux before the calorimeter and closer to the beam pipe, with respect to the multi-wire proportional chambers (MWPC) that are used in the rest of detector. Both the triple-GEM and the MWPC are optimized for fast signal readout and signal yield at 40 MHz, providing the detector information within 20 ns, with a time resolution smaller than 4.5 ns. In particular, only the first three stations are used for transverse momentum measurements, while the last two stations provides binary information whether the particle passed the absorber material or not. For trigger purposes a 5-hit coincidence in all the muon stations allows to identify high-momentum muons.

#### 1.4 LHCb Upgrade I

The LHCb detector will undergo a major upgrade during the Long Shutdown 2, after the completion of Run 2 in October 2018. The Upgrade I is motivated by the necessity to extend the experiment sensitivity on crucial flavour physics observables, that is still limited by the statistics and with the current configuration would need several years of additional data taking. An increase of the instantaneous luminosity to the value  $2 \times$   $10^{33}$  cm<sup>-2</sup>s<sup>-1</sup>, corresponding to a factor five more with respect to the Run 2 conditions, is foreseen. In these conditions the average number of proton-proton collisions at each bunch crossing will be equal to 7.6, leading to higher detector occupancy and radiation level. The maximum readout rate of LHCb is currently limited by the front-end electronics of many sub-detectors: this limitation also strongly motivates the need of a detector upgrade in order to read the full detector at the maximum bunch crossing rate of 40 MHz. The lateral view of the LHCb Upgrade I detector is shown in Fig. 1.6.

Figure 1.6: Lateral view of the LHCb Upgrade I detector.

Sub-detectors as the SPD, PS, and the M1 station of the muon detector will be removed, since they are partly obsolete and can not be operated in the upgraded conditions. The higher luminosity will lead to higher pile-up, number of tracks and irradiation of the detector. This makes necessary an increase of the granularity in order to still be able to reconstruct particles in the detector.

The most relevant modification consists in fully replacing the tracking system. The VELO is replaced with a new version [20] based on hybrid pixel sensors, instead of strip sensors. The upgraded detector is positioned closer to the beam axis in order to improve the impact parameters resolution. The sensors will have a finer granularity with respect to the current design, in order to cope with the higher particle density, primarily in the region closest to the beam axis, arranged in two retractable halves, similar to the current design. The minimum distance from the sensitive are to the beam pipe is 5.1 mm, the pixel size is  $55 \times 55 \ \mu\text{m}^2$ .

The Upstream Tracker (UT) [21] replaces the TT, but maintains a similar layout. It is based on single-sided silicon strip sensors arranged in four layers in *axial-stereo* configuration. The geometrical acceptance at small polar angles is larger and new silicon sensors with improved radiation hardness and finer granularity are mounted near the beam pipe. The front-end electronics have been redesigned in order to perform the readout at 40 MHz rate.

The IT and the OT are replaced by the SciFi Tracker based on scintillating fibres that are read out by silicon photomultipliers. The layout and configuration of the SciFi Tracker is similar to the IT+OT configuration.

The current trigger system, based on both L0 hardware trigger and high level software trigger, is substituted by a full-software trigger. In fact, the L0 trigger on one hand limits the 40 MHz input rate down to 1.1 MHz, while on the other hand becomes inefficient for hadronic events at increased luminosities. The new trigger is able to process events at 40 MHz and take decisions on the basis of the full event information.

Additional information on the LHCb Upgrade I can be found in Ref. [21].

## 1.5 LHCb Upgrade II

As discussed in the previous sections, the LHC will undergo a major upgrade to enter the High Luminosity phase during the Run 4. The LHCb collaboration, aware of the need to fully exploit the flavour physics opportunities of the HL-LHC, proposed a second upgrade, called LHCb Upgrade II to be installed during the LS4 in 2030.

The Expression of Interest for the LHCb Upgrade II is reported in Ref. [22]. The physics case opportunities achievable from the upgrade are reported in Ref. [23].

In the next paragraphs we will report the main contents related to the tracking system upgrade, together with the introduction of precise timing measurements.

With the increase of the instantaneous luminosity the mean number of interactions at each bunch crossing will increase up to  $\mu \approx 50$ , resulting in a significant increase of the total number of tracks to reconstruct per each event. Significant challenges in terms of data rates, reconstruction quality, and increased radiation damage will be faced by old sub-detectors. The collaboration has already identified some potential solutions that would allow the feasibility for the LHCb detector to work in harsher conditions and the introduction of precise timing detectors has been identified as crucial to help the event reconstruction in conditions of increased pile-up and detector occupancy. The use of precise timing will be essential in the tracking detectors, as the VELO, the Upstream, and the Downstream tracking systems. In fact, a resolution of a few tens of ps per particle, will allow charged tracks and photons to be associated with the correct interaction vertex, thereby suppressing the combinatorial background and also allowing for time-dependent CP violating measurements. Moreover, the experiment will also profit from the precise timing in downstream detectors for improving particle identification for low-momentum tracks. Other detector upgrades are proposed such as the replacement of the ECAL with a high granularity tungsten sampling electromagnetic calorimeter, and the instrumentation of the lateral walls of the dipole magnet to significantly increase the detector acceptance for low momentum tracks.

### 1.5.1 VELO sub-detector with timing at high luminosity for the Upgrade II

At the expected conditions of LHCb Upgrade II with instantaneous luminosity of  $2 \times 10^{34} \text{ cm}^{-2} \text{s}^{-1}$ , the expected pile-up is  $\mu \approx 50$ , with a total number of 1500-3500 charged

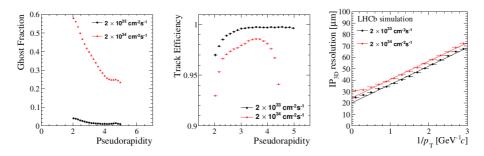

particles within the detector acceptance. The quality of the track and vertex reconstruction performed by the VELO sub-detector will be primarily affected. It is demonstrated that the use of the Upgrade I VELO sub-detector in the Upgrade II environment would not be feasible, leading in particular to a consistent increase of the ghost<sup>2</sup> track rate from 1.6% to 40%. A modest reduction of the tracking efficiency from 99% to 96%, together with a degradation in the impact parameter resolution is expected, as a consequence of the reduced resolution on the primary vertex. Monte Carlo simulation studies for tracking performance at Upgrade II conditions are summarized in Fig. 1.7.

Figure 1.7: Tracking performance of the VELO Upgrade-I sub-detector, with no modifications, at Upgrade I (black points) and Upgrade II (red points) nominal luminosity conditions. Left: ghost fraction as a function of the pseudorapidity. Centre: track efficiency as a function of pseudorapidity. Right: impact parameter resolution as a function of the inverse transverse momentum. Figure from Ref. [22].

Before introducing the precise timing as a viable solution to recover the desired Upgrade I VELO tracking performance, we point out that other less innovative strategies have been considered. As an example, the performance loss can be almost entirely recovered by halving the VELO pixel pitch from the 55  $\mu$ m baseline value to 27.5  $\mu$ m, particularly for the innermost region of the pixel sensors, and by reducing the silicon sensor thickness from 200  $\mu$ m to 100  $\mu$ m. With these modifications the ghost rate ratio can be reduced to the value of 2%, keeping the tracking efficiency to the acceptable value of 96%. Another solution that would benefit the VELO track reconstruction would consist in removing or redesigning the RF foil, present in the Upgrade I VELO. The RF foil is a thin metal shield whose main purpose is to separate the VELO detector vacuum from the LHCb beam vacuum, suppress the wake-fields (produced by the charged bunch) and to reduce the interference from the bunched beams on the detector electronics. It is important to note that the pattern recognition used for this studies has been only coarsely optimized and there could be space for improving the track reconstruction with a better investigation and redesign of the track finding algorithms.

Although the proposed solutions seem encouraging, it is worth investigating the introduction of precise timing in the VELO, and in general in the other tracking detectors. In fact, even if adopting this solution the problem of the mis-association of tracks to their production vertices (PV) and decay vertices would still be present. The identification of band c hadrons is mainly based on the reconstruction of their flight distance, in particular

<sup>&</sup>lt;sup>2</sup>fake tracks reconstructed from spurious hit combinations.

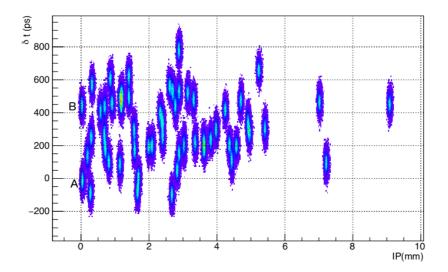

on the presence of a displaced vertex. In conditions of high pile-up, it is easier to incorrectly associate a track from a secondary vertex with a primary vertex from a different ppinteraction, hence reducing the reconstruction quality and degrading the time-dependent CP-asymmetry measurements. Adding the precise time information would resolve this problem by providing an additional coordinate for performing the PV association, which currently relies only on space track parameters (a track is associated with the PV with closest impact parameter value). The PV mis-association could be reduced from 20% down to 5% with a timing precision of 50-100 ps. The distribution of multiple PVs in space and time, as an example, is shown in Fig. 1.8.

Figure 1.8: Distribution of tracks in space and time originated from different PVs. The introduction of timing helps to separate PVs with similar IP values. Figure from Ref [23].

It has been evidenced that the addition of precise timing provides benefits both to track reconstruction and to the PV association. Moreover the addition of timing to the reconstructed tracks would be helpful for other tasks of the event reconstruction, *i.e.* it could be used to improve the association between tracks reconstructed upstream and downstream of the magnet and/or the association of tracks to hits in sub-detectors not directly involved in the tracking reconstruction, as the TORCH that also features precise timing sensors. R&Ds for pixel sensors with precise timing are well motivated and the possibility to have fast-timing sensors with the characteristics required to be used in the upgraded VELO tracker has to be taken in account. In addition, the timing information of the hits can be used at an early reconstruction stage, *i.e.* in the pattern recognition, to reduce the combinatorics of hits from different pp interactions, allowing to relief the computational workload associated with the crowded events expected during the Upgrade II.

#### 1.5.2 Timing in trigger and data processing

At Upgrade II luminosity the LHCb detector is expected to produce data at rates of  $\sim 32$  Tbps [24]. This amount of data has to be processed in real time by the trigger in order to select relevant events. The rate is expected to be reduced by at least 4-5 orders of magnitude before being stored. The projection of technological improvements indicates as feasible the task of moving this volume of data from the detector to the processing farm by the time of Upgrade II. On the other hand, the data processing will be a challenge, with pile-up of  $\mu \approx 50$  and multiple heavy-flavour hadrons produced at every bunch crossing. The traditional trigger strategy based on the selection and the acquisition of bunch crossing events according to inclusive topologies, *i.e.* the presence of a displaced vertex, will no longer be able to significantly reduce the data rate. The Upgrade II data processing strategy should be based on the pile-up suppression providing data reduction by discarding detector hits that are not associated with interesting pp interactions. For this reason there is the necessity to distinguish the reconstructed objects associated with different PVs in a fast manner. The introduction of precise timing in all the sub-detectors would significantly help in this task, in particular mitigating the negative pile-up effects, *i.e.* the PV mis-association being able of separately reconstructing multiple pp events generated within the same bunch crossing. In this scenario, considered the demonstrated ability of LHCb to reconstruct full events with offline-quality in near real-time during Run 2, and considered the technology evolution in the next decade we can consider as feasible the task of triggering at high luminosity also exploiting new computing architectures based on hardware accelerators such as GPGPUs and/or FPGAs to which the IT industry is dedicating a growing interest.

## Fast track finding device for efficient triggering

## 2.1 Challenge of event reconstruction at the High Luminosity LHC

In this section an introduction to the main challenges of event reconstruction and realtime track reconstruction at 40 MHz in the environment of the High Luminosity LHC is provided.

As already introduced, one of the negative effects of the luminosity increase at HL-LHC is given by the increase of the pile-up and the track multiplicity. In the context of the event reconstruction this will result in a consistent slowdown of all the reconstruction algorithm. Moreover the pile-up increase will lead to a loss of physics performance. An already discussed example related to the tracking is the increase of the PV mis-association but effects will be visible in other contexts as the expected decrease of efficiency in the electromagnetic calorimeters, the reduced selection efficiencies for electrons and photons, for hadronic tau decays and b-jets, an expected worsening of the energy resolution for electrons, photons, taus, jets and missing energy.

A key role for profiting of the HL-LHC is to maintain the excellent efficiency in all the LHC experiments, in particular by upgrading the detectors with higher granularity devices and precise timing. Regarding the trigger and the event reconstruction, the increase of the event complexity has to be efficiently handled in order to minimally affect the processing time. Moreover the pile-up increase will lead to the increase of the ratio between interesting and uninteresting events, reducing the fraction of the events that can be discarded. In fact, the traditional trigger systems at LHC are designed to keep or discard the whole bunch-crossing event; this approach becomes unfeasible for growing luminosities. As an example, in a situation of high pile-up with an interesting signature from a single pp the best option would be to identify and store the information; following this approach would result in a strong data reduction but has to be based on a reliable and fast separation of pp interactions within the same bunch-crossing.

## 2.2 Examples of fast track finding devices

Fast track finding devices cover a fundamental role for triggering efficiently on interesting physics processes. Generally they rely on fast pattern recognition and simplified track fitting techniques.

The process of pattern recognition is typically serialized and solved by trials. A simple example of pattern recognition of straight tracks is based on the identification of a *track road* connecting one hit in the first sensor to one hit in the last sensor. Hits compatible with the track road are searched in the intermediate layers and a good track candidate is identified if a minimum number of hits are associated with the track road. On the other hand the process of track finding will fail for many track roads identified from spurious combinations of hits. This process has to be performed for different track roads, whose total number is given in first approximation by the product of hits in the first and last detector layer. In this simplified scenario the algorithm execution time is proportional to the second power of the number of hits. This feature could be problematic in trigger applications where having a fast response is crucial. For this reason parallelized approaches are generally more suitable to be applied to fast tracking devices; moreover solutions based on hardware processing are typically faster compared to software solutions.

In the following, we describe some examples of fast tracking devices that already proved being able to perform fast track reconstruction in HEP experiments with reduced latency and whose information can be included and used in trigger applications, together with proposed R&D for future applications. These solution are based on the use of Associative Memory devices or on the implementation of highly parallelized and pipelined tracking algorithms in Field Programmable Gate Arrays (FPGA).

#### 2.2.1 Pattern recognition in Associative Memory devices

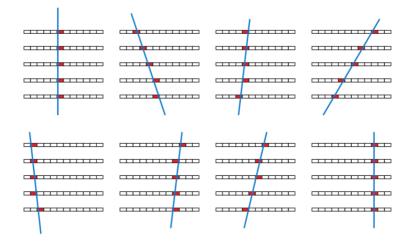

Here we describe the working principle of the pattern recognition using Associative Memories (AM) applied, for sake of simplicity, to the reconstruction of 2-dimensional straight tracks. Let's consider the example of a 2-dimensional tracking system composed of five layers. Each sensor provides the measurement of the track hit position within the layer; we consider each layer to be divided into a limited number of spatial bins defined by  $n_{bins}$ , smaller than the number of channels. In general a track crossing the detector will produce a hit in one bin per layer, as shown in Fig. 2.1.

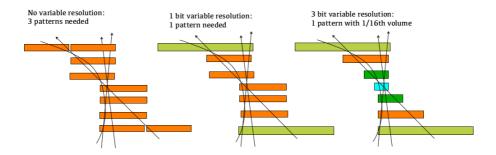

Each bin is identified by its coordinate and we define a *pattern* as a set of bin coordinates corresponding to a possible track. In particular, since the bin size is greater than the spatial resolution there is a *one-to-many* correspondence between patterns and candidate tracks, and different tracks in a reduced region of the track parameter space can match the same pattern. If on one hand the resolution is artificially reduced, on the other hand the number of possible patterns is limited to  $\sim n_{bins}^2$ , while the full track resolution can be recovered in the following steps. Having a limited set of possible patterns, which can be evaluated from simulation, allows to construct the list of all the possible patterns that is called the *pattern bank*, that will be used to perform the task of pattern recognition by comparison of the measured hits in the tracking system to the list of patterns.

Figure 2.1: Examples of straight tracks (blue lines) matching coarse-grained patterns (red segments). Each track produces a hit in one spatial bin per layer; the number of possible patterns is proportional to the number of spatial bins in which the detector layers are divided.

The AM is a particular type of content addressable memory (CAM) in which the pattern bank is stored and can be implemented in custom ASICs. The AM receives the detector hits in input and compares them to the pre-computed patterns; in particular a pattern is matched if all the bins have been activated by at least on hit. For each matched pattern the AM provides the list of the addresses of matching hits in output.

From a practical point of view, all the measured hits are fed to multiple AM chips over which the complete pattern bank is distributed. The AM chips determine in parallel whether the received hits matched one or multiple patterns. The operation is iterated for all the hits and the pattern recognition process completes as soon as the last hit is processed.

It is important to note that the computing time is independent from the size of the pattern bank, while it is proportional to the time needed to read out and deliver the hits from the detector. The pattern and the hits provided in output from the AM are finally used to perform the track fitting in the following stage of processing, eventually discarding candidate tracks obtained from spurious combinations of hits.

As previously pointed out, the size of the detector bins has to be tuned in order limit the size of the pattern bank and optimized according to the expected trajectories evaluated from simulations. As stated before, the coarse resolution of the patterns does not allow to directly estimate the track parameters but provides a good hint of the track trajectory, since the hits lie in a limited range of coordinates; this makes possible to apply simplified fitting techniques, as the *linearized track fitting*, to evaluate the track parameters. Examples of systems using the AM are the Silicon Vertex Trigger (SVT)[25] of the Collider Detector at Fermilab (CDF)[26], and the Fast TracKer (FTK)[27] of the ATLAS experiment.

#### 2.2.2 Silicon Vertex Trigger at CDF

Here we provide a brief description of the CDF experiment, which implemented a fast tracking device based on Associative Memories for fast track reconstruction, as part of the trigger decision chain.

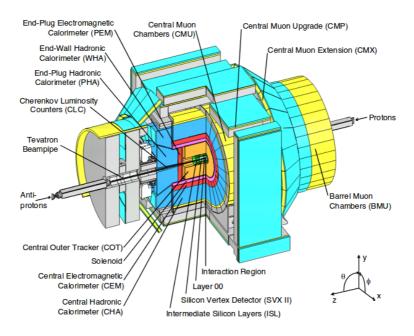

**CDF detector** A scheme of the CDF detector is shown in Fig. 2.2.

Figure 2.2: Scheme of the CDF detector.

The CDF is a cylindrical detector based on multiple layers of sub-detectors organized as follows, with increasing radius: the Silicon Tracking System and the Central Outer Tracker (COT) placed between the beam pipe and the solenoid magnet, the Electromagnetic and Hadronic Calorimeters and the Muon Detectors placed after the magnet. The solenoid magnet is located at 1.5 m from the beam line, and provides a uniform magnetic field of 1.4 T that is needed for the particles momenta measurement.

The Silicon Tracking System is composed of three concentric cylindrical sub-detectors, the Innermost Silicon Layer (L00), the Silicon Vertex Detector (SVXII) and the Intermediate Silicon Layer Detector (ISL); all of them are based on silicon strip sensors. The L00 layer is placed at a distance of 13.5 mm from the beam axis. The SVXII is based on three layers of double-sided silicon sensors to provide 3-dimensional measurement of the track hits; it is placed at a distance from the beam axis between 25 mm and 106 mm. The ISL is based on three layers of sensors at distances of 200, 220, 280 mm. The Silicon Tracking System has a total of eight layers of sensors measuring the hits position with a resolution of 10  $\mu$ m and the impact parameter with 40  $\mu$ m resolution, with a total pseudorapidity coverage of  $|\eta| < 2$ . The system covers a crucial role in the identification of *b* hadrons

since their typical signature is given by the presence of a displaced vertex with respect to the primary vertex of the  $p\bar{p}$  collision.

The COT is dedicated to tracking at larger distances from the beam axis ( from 400 mm to 1370 mm ). It is a drift chamber with sensing wires in *stereo* configuration, with half of the wires oriented along the beam axis and half tilted by  $\pm 2^{\circ}$  angle. Tracks in the COT are reconstructed by first identifying three hits compatible with a particle trajectory from the interaction point, adding further hits near the track projection and finally fitting the hits with a five parameter helix. The COT tracks are projected to evaluate the expected position of the hits in the Silicon Vertex Detector and the two best candidate hits in each layer are linked to the COT track. The final track is obtained by selecting the one with best fit by mean of a  $\chi^2$  minimization algorithm.

The Electromagnetic and Hadronic Calorimeters measure the energy of particles and jets from hadronization and they are based on alternating layers of scintillators with lead and steel absorbers, respectively. The particles interact in the absorber and produce a shower of lower energy particles that are converted into photons in the scintillators, whose light is collected by photomultiplier tubes.

The Muon Detectors represent the last layer of sub-detectors; they are based on drift chambers and arranged in multiple sub-systems covering different geometrical acceptances.

**CDF Trigger System and Silicon Vertex Trigger** The CDF Trigger System is based on three levels of processing. Level 1 and Level 2 are completely implemented in hardware while Level 3 is implemented in software. The CDF trigger provides a strong data reduction through fast identification of distinctive signal signatures, many of them are based on the fast track reconstruction of charged-particles in the bending plane of the spectrometer. The event rate is reduced from 2.5 MHz, corresponding to the Tevatron bunch crossing frequency, to 30 KHz at the Level 1, and down to 300 Hz at the Level 2. The Level 1 trigger requires at least two COT tracks, reconstructed by the *eXtremely Fast Track processor* (XFT), providing 2-dimensional tracks measured in the plane transverse to the beam axis. The tracks are matched to the silicon hits from the SVXII by the Silicon Vertex Trigger (SVT) that is part of the Level 2 trigger. The Level 2 requires at least a 120  $\mu m$  impact parameter, defined as the distance of a track from the primary vertex. The Level 3 provides a full software confirmation of the previous selection reducing the rate to 75 Hz.

The SVT is an example of fast tracking device able to provide reconstructed tracks with 35  $\mu m$  impact parameter resolution, performing the full tracking in ~ 15  $\mu$ s. The same algorithm implemented in software would require ~ 0.1 s, considering the computing power at the time of the experiment[25]. This is possible thanks to a highly parallelized and pipelined architecture, in particular using the AM and performing the track fit in FPGAs.

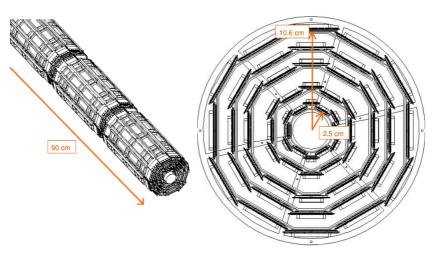

The SVT receives and processes the hits from the SVXII sub-detector, whose scheme is shown in Fig. 2.3.

The SVXII has a cylindrical symmetry and can be divided in 12 angular wedges, each of them can be processed independently by dedicated hardware; this feature allows a

Figure 2.3: Scheme of the SVXII sub-detector.

first level of parallelization of the processing. The presence of tracks in the COT and compatible hits (based on the COT track projection to the SVXII) is required to start the reconstruction of tracks in the SVXII by the Silicon Vertex Trigger system. Each sensor layer is divided in programmable width bins, typically 250 – 700  $\mu m$ , while the COT track projection to the outer radius of the SVXII are considered as an extra (virtual) layer, with typical bin size of 3 mm. A pattern bank of 32K most probable patterns is computed offline based on Monte Carlo simulation and loaded into the AM system. The SVT compares the measured hits to the pattern bank an the AM system provides the valid patterns together with the hits of each identified candidate tracks, which are fitted using a linearized track fitting algorithm performed in FPGAs.

#### 2.2.3 Fast Tracker at ATLAS

Here we provide a brief description of the ATLAS tracking system and the trigger system together with the description of the Fast Tracker (FTK), a fast tracking device based on Associative Memories providing the reconstructed tracks to the high level trigger.

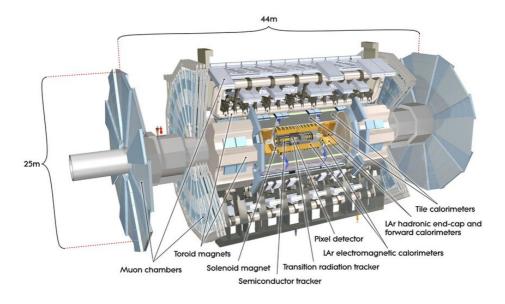

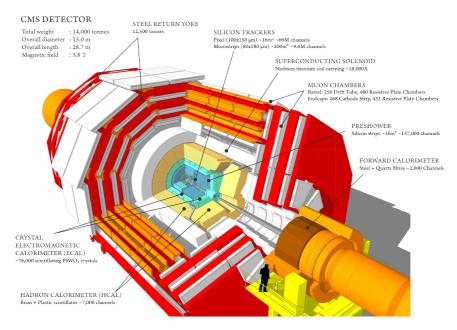

ATLAS detector A scheme of the ATLAS detector is shown in Fig. 2.4.

The ATLAS is a cylindrical detector composed of the following sub-detectors: the Inner Detector, the Calorimeters, the Forward Detectors, the Muon System.

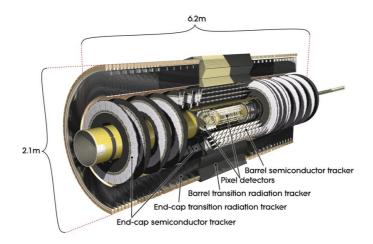

The Inner Detector is the main tracking system: it is based on different sub-systems and its scheme is shown in Fig. 2.5.

The Insertable B-Layer (IBL) is the first detector layer, featuring pixel sensors based on different technologies. In the *barrel* region, whose minimum and maximum radius are 31 mm and 40 mm, 3D pixel sensors are used due to the higher radiation tolerance while in the *end-cap* regions it features planar pixel sensors. The pixel size is  $50 \times 250 \ \mu m^2$  for both types of sensors. The IBL is an extra detector added during LS1 to improve the track and vertex reconstruction provided by the Pixel Detector, dedicated to precise

Figure 2.4: Scheme of the ATLAS detector.

Figure 2.5: Scheme of the ATLAS Inner Detector.

vertex reconstruction. The Pixel Detector is based on silicon pixel sensors and is arranged in three concentric barrel layers at distances of 50.5 mm, 88.5 mm, 122.5 mm from the beam axis and four disks, orthogonal to the beam axis, to complete the angular coverage. The pixel size is  $50 \times 400 \ \mu\text{m}^2$ . The Semi-Conductor Tracker detector (SCT) is positioned after the Pixel Detector and is composed of four layers at 299 mm, 371 mm, 443 mm and 514 mm from the beam axis; these layers are based on silicon strip sensors arranged in stereo configuration. Two groups of nine disks each, based on tapered sensors, complete the angular coverage. The Transition Radiation Tracker (TRT) is the outermost tracking detector. It is based on straw tube detectors, combining both tracking and particle identification capabilities.

The Calorimeter system is composed of the Liquid Argon calorimeter and the Tile hadronic calorimeter, both placed after the solenoid magnet. The first features both electromagnetic and hadronic calorimeter functions either in the barrel region and in the end-cap regions. The Tile calorimeter is a hadronic calorimeter based on scintillating tiles and iron absorbers.

The Muon system is the outermost sub-detector and provides the momentum measurements for muons using the track deflection by three large superconducting magnets. Muon tracks are measured in three cylindrical layers both in barrel and forward/backward regions.