## UNIVERSITÀ DEGLI STUDI DI MILANO

Ph.D in Computer Science – XXXI cycle Department of Computer Science "Giovanni Degli Antoni" Settore scientifico disciplinare: INF/01

# Design and Synthesis of High Density Integrated Circuits

Ph.D Thesis of: Luca Frontini

Tutor: Dr. Gabriella Trucco Co-tutor: Prof. Valentina Ciriani

Ph.D school coordinator: Prof. Paolo Boldi

Academic year 2017-2018

#### Abstract

Gordon E. Moore, a co-founder of Fairchild Semiconductor, and later of Intel, predicted that after 1980 the complexity of an Integrated Circuit (IC) would be expected to double every two years. The prevision made by Moore held for decades, for this reason it is also called "Moore's law".

The trend in ICs is driven by a reduction of area and power consumption. Today scaled CMOS technologies are the main solution for digital processing. However, the interconnection scaling is not optimal. At every new technology node, the number of metal layers and their thickness increases, exploiting the vertical direction. The reduction of the minimum distance between interconnections and the growth in vertical dimension increase the parasitic capacitance and consequently the dynamic power consumption. Moreover, due to the non-optimal scaling of the interconnections, signal routing is becoming more and more challenging at every technology node advancement. Very scaled technologies make possible to reach a great transistor density. However, the design must comply to strict rules for metal interconnections.

The aim of this thesis is to find possible solutions to the disadvantages of scaled CMOS technologies. This goal is obtained in two different ways: using ad-hoc design techniques on today CMOS technologies and finding new approaches to logic synthesis of nanocrossbars, that are an emerging post-CMOS technology. The two approaches used corresponds to the two parts of this thesis.

The first part presents the design of an Associative Memory (AM) focusing the attention on develop design and logic synthesis techniques to reduce power consumption. The field of applicability of AMs is real-time pattern-recognition tasks. The possible uses range from scientific calculations to image processing for intelligent autonomous devices to image reconstruction for electro-medical apparatuses. In particular AMs are used in High-Energy Physics (HEP) experiments to detect particle tracks. HEP experiments generate a huge amount of data, but it is necessary to select and save only the most interesting tracks. Being the data compared in parallel, AMs are synchronous ICs that have a very peaked power consumption, and therefore it is necessary to minimize the power consumption. This AM is designed within the projects IMPART and HTT in 28 nm CMOS technology, using a fully-CMOS approach. The logic is based on the propagation of a "kill signal" that, if one of the bits in a word is not matching, inhibits the switching of the following cells. Thanks to this feature, the designed AM array consumes less than 0.7 fJ/bit. A prototype has been fabricated and it has proven to be functional. The final chip will be installed in the data acquisition chain of ATLAS experiment on HL-LHC at CERN.

In the future nanocrossbars are expected to reduce device dimensions and interconnection complexity with respect to CMOS. Logic functions are obtained with switching lattices of four-terminal switches. The research activity on nanocrossbars is done within the project NANOxCOMP.

To improve synthesis are used some algorithmic approaches based on Boolean function decomposition and regularities, in particular P-circuits, EXOR-Projected Sums of Products (EP-SOP), Dimension-reducible (D-RED) functions and autosymmetric functions. The decomposed functions are implemented into lattices using internal and external decomposition methods. Experimental results show that this approaches reduce the complexity of the single synthesis problem and leads, in average, to a reduction of lattice area and synthesis time. Lattices are made of self-assembled structures and they have a non-negligible defectivity ratio. To cope with this limitation, are presented some techniques to reduce sensitivity to defects.

ii

# Contents

| 1 | Intr | oductio  | n                                     | 1  |

|---|------|----------|---------------------------------------|----|

|   | 1.1  | CMOS     | S technology                          | 4  |

|   | 1.2  | Switch   | hing lattices                         | 5  |

|   | 1.3  | Thesis   | s Organization and Overview           | 6  |

|   |      | 1.3.1    | Part I: Scaled CMOS Technology        | 6  |

|   |      | 1.3.2    | Part II: Switching Lattices           | 7  |

| I | Sca  | led CN   | IOS Technology                        | 9  |

| 2 | Scal | ed fabr  | rication processes                    | 11 |

|   | 2.1  | Techn    | ologies and materials                 | 12 |

|   |      | 2.1.1    | High-ĸ dielectrics                    | 12 |

|   |      | 2.1.2    | Regular Patterns                      | 13 |

|   | 2.2  | Scalin   | g issues                              | 14 |

|   |      | 2.2.1    | Variability                           | 14 |

|   |      | 2.2.2    | Interconnection capacitances          | 14 |

|   |      | 2.2.3    | Digital Switching Noise               | 16 |

| 3 | Asso | ociative | Memory ICs                            | 19 |

|   | 3.1  | AM cl    | hip road-map                          | 21 |

|   | 3.2  | AM cl    | hip architecture and functionality    | 23 |

|   |      |          | Write mode                            | 23 |

|   |      |          | Compare mode                          | 23 |

|   |      | 3.2.1    | Variable resolution                   | 24 |

|   |      | 3.2.2    | AM chip required specifications       | 25 |

|   | 3.3  | KOX(     | DRAM Associative Memory Cell for AM07 | 25 |

|   |      | 3.3.1    | Schematic Diagrams and Layout         | 28 |

|   |      | 3.3.2    | KOXORAM cell working modes            | 28 |

|   |      | 3.3.3    | Clockless logic                       | 28 |

|   |      | 3.3.4    | Simulations                           | 30 |

## CONTENTS

|    |            | 3.3.5   | Measurements                    |   |

|----|------------|---------|---------------------------------|---|

|    | 3.4        | Improv  | vements for AM08                |   |

|    |            | 3.4.1   | Hi performance technology       |   |

|    |            | 3.4.2   | KOXORAM+ 32                     |   |

|    |            | 3.4.3   | SRAM metastability 33           |   |

|    |            |         | Butterfly diagram               |   |

|    |            |         | SRAM design                     |   |

|    | 3.5        | Quorui  | m circuit                       |   |

|    |            | 3.5.1   | Simulation Results              |   |

|    |            | 3.5.2   | Design Verification             |   |

|    | 3.6        | Digital | ly Controlled Oscillator        |   |

|    |            | 3.6.1   | Circuit Structure               |   |

|    |            | 3.6.2   | Layout Design                   | I |

|    |            | 3.6.3   | Simulations                     |   |

|    |            |         |                                 |   |

| II | Sw         | itahina | Lattices 51                     |   |

| 11 | <b>G</b> W | nunng   | Lattices 51                     |   |

| 4  | Tech       | nology  | Description 53                  |   |

|    | 4.1        | Boolea  | n function implementation       |   |

|    | 4.2        | Synthe  | sis methods                     | l |

|    |            | 4.2.1   | Altun-Riedel 56                 | l |

|    |            | 4.2.2   | Gange-Søndergaard-Stuckey       |   |

| _  | D          | • / •   |                                 |   |

| 5  |            | -       | ion Methods 59                  |   |

|    | 5.1        |         | its and EP-SOP forms            |   |

|    |            | 5.1.1   | P-circuits                      |   |

|    |            | 5.1.2   | EXOR-Projected Sums of Products |   |

|    | 5.2        |         | cible Boolean functions         |   |

|    | 5.3        |         | mmetric functions               |   |

|    | 5.4        |         | l Composition                   |   |

|    |            | 5.4.1   | P-Circuits                      |   |

|    |            | 5.4.2   | EXOR-Projected-Sums Of Products |   |

|    |            | 5.4.3   | D-Reducible functions           |   |

|    |            | 5.4.4   | Experimental Results            |   |

|    |            |         | P-circuits and EP-SOP           |   |

|    | _          |         | D-Reducible functions           |   |

|    | 5.5        |         | al Composition                  |   |

|    |            | 5.5.1   | Autosymmetric functions         |   |

|    |            | 5.5.2   | P-Circuits                      | , |

iv

| CONTENTS |

|----------|

|----------|

|     | 5.6    | 5.5.3 D-Reducible functions      | 93<br>94 |

|-----|--------|----------------------------------|----------|

| 6   |        | -                                | 101      |

| v   | 6.1    |                                  | 101      |

|     |        | Defect Injection Methodology     |          |

|     | 6.2    | 5 5                              | 102      |

|     |        | 6.2.1 Benchmarks and Simulations | 102      |

|     | 6.3    | Mitigation by Defect Avoidance   | 104      |

| 7   | Con    | clusions                         | 107      |

|     | 7.1    | Concluding remarks               | 107      |

|     | 7.2    | -                                | 109      |

|     | 7.3    | *                                | 109      |

|     | 1.5    |                                  | 109      |

| Ар  | pend   | ices                             |          |

| A   | AM     | chip specifications              | 111      |

|     | A.1    | Main requirements                | 111      |

|     |        | Aggressive goals                 | 112      |

|     |        | Full Custom simulation Corners   | 112      |

|     |        | Interdisciplinary Applications   | 112      |

|     |        | A.1.1 Cores                      | 113      |

| Bil | bliogr | aphy                             | 116      |

| List of | Terms |

|---------|-------|

|---------|-------|

127

## Chapter 1

# Introduction

From 1952 to 1956, Willard V. Quine [1, 2] and Edward J. McCluskey [3] developed a new algorithm to minimize Boolean functions, called Quine-McCluskey algorithm.

At that time, logic circuits were built using discrete components. Quine-McCluskey algorithm aims at minimizing the number of literals, and so the devices, needed to synthesize a Boolean function. The minimization of device number was a strong requirement to build digital circuits because it permits to reduce the cost related to the components and to mitigate the problem of heat dissipation.

In 1958, Jack S. Kilby showed the first working Integrated Circuit (IC) [4] to Texas Instruments managers, for the first time electronic components were integrated onto a single substrate. The technology used to build ICs was the first step to extend the use of transistors into mass-produced electronic circuits and microprocessors, indeed in a few years the number of component inside a single IC grew up to more than one hundred integrated devices.

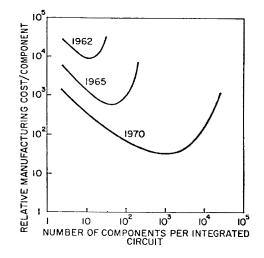

Gordon E. Moore, a co-founder of Fairchild Semiconductor, and later of Intel, wrote in an article published in 1965 [5]: "The complexity for minimum component costs has increased at a rate of roughly a factor of two per year (Figure 1.1). Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least ten years".

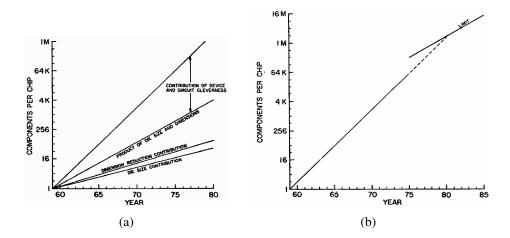

Later, in 1975, Moore revised his forecast [6] predicting that after 1980 the rate of increase of complexity can be expected to double every two years instead of one, as Figure 1.2 shows. He wrote that it was due to a reduction of "circuit and device cleverness" that are particular production and design techniques, that permit to improve device density.

The prevision made by Moore held for decades, for this reason the plot in Figure 1.2b is also called "Moore's law".

The increasing density of ICs was obtained also using a new device: the Metal-

Figure 1.1: Plot of relative manufacturing cost per component, published by G. Moore in [5].

Figure 1.2: (a): approximate component count for complex integrated circuits vs. year of introduction. (b): projection of the complexity curve reflecting the limit on increased density through invention. Published by G. Moore in [6].

Oxide-Semiconductor Field-Effect Transistor (MOSFET). The MOSFET was discovered by Julius E. Lilienfeld in 1925 and integrated into an IC by D. Kahng and Martin M. Atalla at Bell Labs in 1959. The MOSFET was described by Moore in 1965 as a promising device for future digital ICs [7] because a MOSFET can scale better than a Bipolar Junction Transistor (BJT) indeed MOSFET construction is planar and can be easier integrated into fabrication processes.

With the implementation of Complementary Metal-Oxide Semiconductor (CMOS) technology, that uses p-MOS and n-MOS transistors instead of resistors as pullup and pull-down, the BJT was almost completely substituted by MOS in digital ICs. CMOS logic has less static power than BJT logic and pull-up and pull-down resistors, are not necessary. This aspects led to the diffusion of CMOS because they permit to fabricate low power consuming ICs that also present a higher device density.

MOS transistor size has been scaled for decades in an almost regular way, according to the Moore's law [8, 9]. The trend in ICs is driven by a reduction of area and power consumption. Today scaled CMOS technologies are the mainstream solution for digital processing.

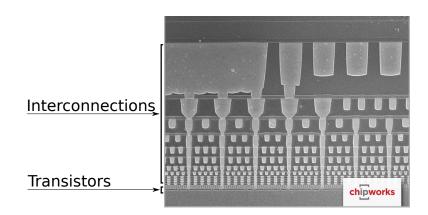

However, the interconnection scaling is not optimal [11, 12]. At every new technology node, the number of metal layers and their thickness increases, exploiting the vertical direction, as Figure 1.3 shows. The reduction of the minimum distance between interconnections and the growth in vertical dimension increase the parasitic capacitance and consequently the dynamic power consumption. Moreover, due to the non-optimal scaling of the interconnections, signal routing is becoming more and more challenging at every technology node advancement, and it is limiting IC performances.

Figure 1.3: Cross section of Intel 14 nm CMOS technology [10].

## 1.1 CMOS technology

Very scaled technologies make possible to reach a great transistor density. However, the design must comply to strict rules for metal interconnections, and the reduction of interconnections is more important than reduction of the number of components, to optimize area and power consumption.

Today, to implement complex production-grade logic ICs it is necessary to deal with the disadvantages of scaled CMOS technologies and mitigate them with ad-hoc design techniques.

One of the applications where scaled CMOS technologies are used are Content Addressable Memories (CAMs). CAMs write data at an address and then, during comparison tasks, find addresses that match data. CAMs can be used for sparse database search, cache or routing table.

Associative Memories (AMs) are a particular type of CAMs [13] because AMs can handle also segmented data. The field of applicability of AMs is real-time pattern-recognition tasks. The possible uses range from scientific calculations to image processing for intelligent autonomous devices to image reconstruction for electro-medical apparatuses.

In particular, AMs are used in High-Energy Physics (HEP) experiments to detect particle tracks; the track of a particle is the path that a charged particle follows as it transverses the various layers of the detector. HEP experiments generate a huge amount of data, but not all the data are stored offline. The decision to store the data, or not, is taken online by the trigger system of the experiment. For best results in identifying interesting data and rejecting non-interesting ones, track identification and reconstruction is often needed early in the trigger chain, when the data rate is still high. In order to identify the tracks, AMs are used in the acquisition chain to find a correlation between the input data coming from the detector pixels and a set of pre-stored data [14, 15], for this reason they have to respect strict requirements of timing and power consumption. Being the data compared in parallel, AMs are synchronous ICs that have a very peaked power consumption, with peaks aligned with the rising edge of the clock.

There are four critical factors, described above, for AM and more in general for CMOS ICs:

- 1. signal routing and interconnections are critical due to scaling;

- reduction of interconnections is more important than reduction of components;

- 3. AM power consumption is peaked and need to be minimized;

- 4. AM has to satisfy the specifications given by the trigger system.

This thesis describes the research activities within the projects IMPART<sup>1</sup> [16] and HTT<sup>2</sup> [17]. The final chip will be implemented in the data acquisition chain of ATLAS ("A Toroidal LHC ApparatuS") [18] experiment in the High Luminosity Large Hadron Collider (HL-LHC) at Conseil Européen pour la Recherche Nucléaire (CERN).

## **1.2** Switching lattices

In future, the Moore's law will stop to be valid [11]. The only way to improve speed, area, and power consumption will be to go over CMOS, by adopting new technologies. One of the emerging post-CMOS technologies are nanocrossbars [19].

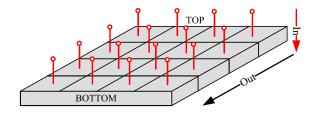

Nanocrossbars arrays are fabricated with relatively cheap bottom-up nanofabrication techniques rather than using purely lithography based conventional production [20, 21, 22]. Due to the novel manufacturing techniques, fabric yields to be in regular and dense form [23]. Because of their structure and technology, they are area and power efficient but they have a non-negligible defectivity ratio. Logic functions are obtained with arrays of crossbar-type switches. This structure is expected to reduce device dimensions and interconnection complexity with respect to CMOS.

Logic synthesis on nanocrossbars is one of the most important steps that are necessary to utilize this technology instead of CMOS [24]. Nanocrossbars requires different tools with respect to CMOS, due to the different type of switches. In literature there are described two possible algorithms to synthesize Switching lattices. The first one, developed by Altun and Riedel [25] produces lattices with a size that grows linearly with the number of products of the starting Boolean function, it runs in time that grows polynomially in the number of ISOP. The second algorithm, developed by Gange, Søndergaard and Stuckey [26], uses a SAT-solver, it provides minimum area lattices, but it uses a considerable amount of time and resources.

As described above there are some interesting nanocrossbars peculiarities:

- 1. they are an emerging post-CMOS technology;

- 2. they are area and power efficient;

- 3. the optimum synthesis requires a considerable amount of time and resources;

<sup>&</sup>lt;sup>1</sup>Innovative Multi-chip system for multi-purpose PAttern Recognition Tasks (IMPART) is a project that consists in developing a cutting edge pattern recognition device for fast image analysis and future trigger processors for HEP experiments.

<sup>&</sup>lt;sup>2</sup>Hardware Tracking for the Trigger (HTT) is a Hardware-based Tracking for the ATLAS Trigger, based on custom-designed AM ASICs for pattern recognition and FPGAs for track reconstruction and fitting.

4. they have a non-negligible defectivity ratio;

This thesis describes the work done within the project NANOxCOMP<sup>3</sup>, that aims to develop a complete synthesis methodology for nanoscale switching crossbars that leads to the design and construction of an emerging computer [27].

## **1.3 Thesis Organization and Overview**

Moore's law is holding for decades, but its end is approaching. The major problems of today scaled CMOS technologies are interconnection capacitance and routing complexity.

Therefore the aim of this thesis is to to find possible solutions to the disadvantages of scaled CMOS technologies.

This results are obtained using two different approaches: I) designing a commercialgrade AM IC finding solutions to mitigate power consumption and routing problems; II) developing nanocrossbars synthesis tools to improve the integration process. In this way, it is possible mitigate current CMOS issues and, in the mean time, find synthesis techniques for nanocrossbars to provide a proper synthesis tool set when the fabrication processes will be suitable for mass-adoption.

### 1.3.1 Part I: Scaled CMOS Technology

This part is focused on scaled CMOS technologies, that today are the main solution for digital processing. Then are analyzed their peculiarities to find design and synthesis approaches that can be useful to design digital circuits, in particular AMs.

**Chapter 2** analyzes scaled CMOS fabrication processes. The description helps to identify the characteristics that can be exploited for the synthesis and the design, such as the great device density, and the issues that is possible to mitigate, for instance the non optimal interconnection scaling and the particular layout rules related to fabrication processes.

**Chapter 3** is focused on AM ICs. First are described some possible applications of AMs. This description is useful to understand some design peculiarities and the required specifications of timing and power consumption. Then are described the AM chip architecture and the function of each logic block. The specifications of the AM chip are published in [28]. Then it describes the design of an AM cell that reduces power consumption with respect to previous solutions, using a logic

6

<sup>&</sup>lt;sup>3</sup>NANOxCOMP has received funding from the European Union's H2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 691178.

#### 1.3. THESIS ORGANIZATION AND OVERVIEW

synthesis approach aiming at reducing interconnections instead of the number of transistors. The cell is designed in 28 nm CMOS technology, using a fully-CMOS approach. The designed AM cell permits, during comparison, to send a "kill" signal to the cascaded cell to inhibit further switching if one of the input bits is not matching the pre-stored data. Thanks to this feature, the CAM array requires less than 0.7 fJ/bit per comparison and reaches a comparison frequency of 184 MHz. Than are describes the layout design, the simulations that have been done to test the SRAM metastability and the design techniques that used to avoid it.

Than are described the two blocks that will be included into the next test chip to further improve the memory density and reduce the power consumption of the AMs: the quorum circuit an the Digitally Controlled Oscillator(DCO). The quorum circuit orders the outputs of the memory arrays and has a logic based on a divide and conquer sorting algorithm. It will substitute the former standard cell circuit occupying less silicon area. The DCO uses logic gates as delay elements to mitigate the mismatch of scaled CMOS technology, it is used to spread the AM clock to reduce the current peak due to AMs. The AM cells and the test of AM07 are published in: [29, 30, 31]. The population count circuit is published in [32, 33]. The DCO is published in [34]

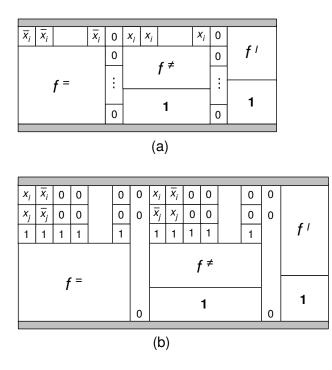

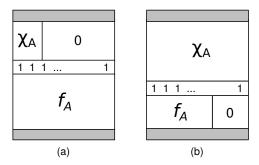

## **1.3.2** Part II: Switching Lattices

Switching Lattices are an emerging technology that can solve some issues of scaled CMOS technology. The synthesis of minimal Switching lattices is time and resource intensive and can fail to synthesize the lattice in a reasonable amount of time. For this reason, this part shows some methods aimed at reducing computing time and lattice area, and describes some techniques for mitigating lattice faults.

In **Chapter 4** describes the synthesis tools that today are used for switching lattices. The description permits to show the peculiarities of each method.

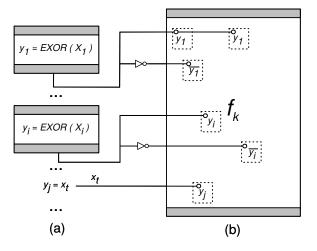

In **Chapter 5** studies an algorithmic approach to switching lattices based on Boolean functions decomposition methods and regularities: P-circuits, EXOR-Projected Sums of Products (EP-SOP), Dimension-reducible (D-RED) functions and autosymmetric functions. It shows two different approaches to implement the decomposed functions into lattices: internal and external decomposition. Internal decomposition implements all the sub-lattices into one single lattice. External decomposition uses a two level approach and requires additional inverters and routing.

A large set of experimental results is presented showing in average an area and synthesis time gain. The external decomposition method can obtain lattices that

have a total area smaller than the optimum single lattice. Internal decomposition results on P-circuit are published in [35] and D-red are published in [36]. The article that compare the decomposition methods is [37]. External decomposition results on autosymmetric functions are published in [38]. The comparison between external decomposition is published in [39].

In **Chapter 6** enunciates a metric for sensitivity analysis of switching lattices that takes in account SA0 and SA1 faults. Then, it shows several methodologies that exploit the regularities of synthesis algorithms aimed at mitigating the lattice defects. Part of this chapter is published in [40].

Part I

**Scaled CMOS Technology**

## **Chapter 2**

# **Scaled fabrication processes**

Microelectronic device industries invest a lot of resources to find novel technologies to increase device density and circuit speed minimizing power consumption. This is done optimizing the CMOS production process changing the fabrication procedures and the materials used to build the devices [9].

The classic scaling (shown in Figure 2.1), described in [12] by R. Dennard in 1975, cannot be strictly applied to production nodes under 130 nm [41], some technology improvements are needed. Often below this threshold there were done previsions of scaling problems due to technology limitations, materials or productive processes, but then technology improvements and fabrication process modifications succeeded into overcoming these limits.

The increase of device density and the adoption of new materials and fabrication procedures requires some modification on design and synthesis of digital circuits, in particular it is necessary to take into account the power consumption.

| Device or circuit parameter | Symbol                 | Scaling factor |                                    |

|-----------------------------|------------------------|----------------|------------------------------------|

| Device dimensions           | $t_{ox}, L, W$         | 1/k            | Voltage, V – Winnig (              |

| Doping concentration        | $N_a$                  | k              |                                    |

| Voltage                     | V                      | 1/k            | Gate ↓ ←W→                         |

| Current                     | Ι                      | 1/k            | source                             |

| Capacitance                 | $\varepsilon A/t_{ox}$ | 1/k            |                                    |

| Delay time                  | VC/I                   | 1/k            | ← L→                               |

| Power dissipation           | VI                     | $1/k^{2}$      |                                    |

| Power density               | VI/A                   | 1              | p Substrate, doping N <sub>A</sub> |

Figure 2.1: Traditional MOSFET scaling as described by Robert Dennard, published by Bohr and Young in [9]

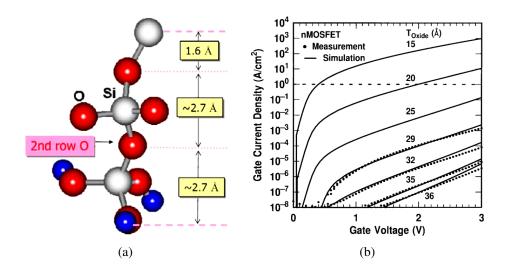

Figure 2.2: (a) Graph of the oxide leakage current versus gate voltage per different oxide thickness. The oxide leakage current increases exponentially as the oxide thickness reduced linearly [43]. (b) Bonding structure of SiO<sub>2</sub> indicating the minimum thickness of the bulk oxide is about 7 Å [42].

## **2.1** Technologies and materials

In this section we describe the principal technologies used by scaled CMOS technologies.

#### 2.1.1 High-K dielectrics

For decades silicon oxide (SiO<sub>2</sub>) was used to build the gate oxide of MOSFETs. The downsizing of MOS follows the rules shown in Figure 2.1: all the voltages and dimensions are reduced by a factor k. To have an electric field of the scaled transistor equal to the large device, the charge density, and so the oxide capacity  $(C_{ox})$ , have to be up-scaled by k.

The approach used approximately until 64 nm process was to the reduce oxide thickness. In 28 nm and smaller technology nodes the needed thickness would be near the minimum thickness of SiO<sub>2</sub>, 7 Å [42], that corresponds to two layers of SiO<sub>2</sub> atoms, as Figure 2.2a shows. Moreover the oxide leakage current increases exponentially as the oxide thickness reduces linearly, as Figure 2.2b shows [43]. For this reason MOSFET with thin oxides are not suitable for low power circuits.

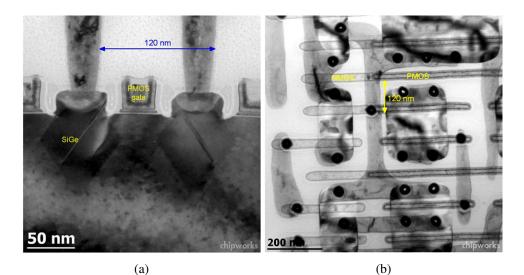

Either the physical and the technological constraints can be circumvented by replacing the ultra-thin SiO<sub>2</sub> with physically thicker high- $\kappa$  materials. But the most promising high- $\kappa$  material, the hafnium oxide HfO<sub>2</sub>, presents problems due to the interface between silicon and insulator, to provide better results it is used the hafnium-silicon oxinitride (HfSiON). HfSiON is obtained by atomic layer deposition to improve the oxide thickness uniformity. Figure 2.3a shows a PMOS

Figure 2.3: (a) Altera 5SGXEA7K2F40C2 Stratix V 28 nm HP PMOS, TEM photograph [45]. (b) Xilinx XC7K325T Kintex-7 TSMC 28 nm HPL, Plan View TEM photography [45], different types of metals are used to fabricate PMOS and NMOS gates

in 28 nm TSMC technology, that uses high- $\kappa$  dielectrics. HfSiON is not compatible with polysilicon gate, for this reason it is used a metal gate electrode, made by titanium nitride (TiN) for P-MOS and a titanium aluminum nitride (TiAlN) for N-MOS gate [44]. In Figure 2.3b it is possible to notice the two different types of material used to fabricate MOS gates.

## 2.1.2 Regular Patterns

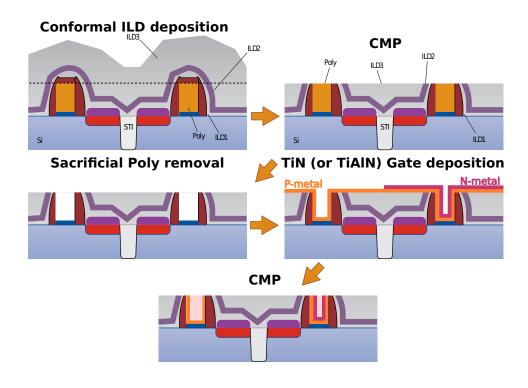

Gates are fabricated using a gate-last approach, called also *damascene*. This fabrication procedure guarantee a precise gate alignment and make possible to use different types of metals for PMOS and NMOS. Gate-last approach uses sacrificial polysilicon gate structures that are substituted with the MOS metal gate.

The fabrication process is shown in Figure 2.4, from top-left to bottom-right:

- Deposition of Inter Layer Dielectric (ILD) over the sacrificial gate structures.

- Chemical Mechanical Polishing (CMP) to planarize the wafer.

- The sacrificial polysilicon is removed using a chemical attack.

- It is deposed a TiN gate for PMOS and a TiAlN gate for NMOS.

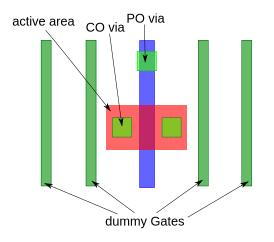

CMP is a critical polarization procedure because it is required to have a minimum material density to provide a good planarization without damaging the structures below the planarization level. For this reason it is necessary to use dummy gate structures to have a good planarization. Dummy gates, as Figure 2.5 shows, are gate structures that does not intersect active area.

Transistor gates are build using phase shift masks [46, 47, 48]. In this way it is possible to create structures that are smaller than the wavelength of the light source used for the photolithography. Dummy gates are useful also for phase shift lithography because this techniques exploit light interference phenomena to create the gates and the most external gates of the interference figure may present some defects.

## 2.2 Scaling issues

Very scaled transistors permit to have great device density, but the process shrinking can lead to variability problems. Moreover interconnections do not scale as well as transistors increasing routing complexity and interconnection capacitances.

#### 2.2.1 Variability

Scaled technologies presents a non-negligible process variability. The two main sources of variability are local mismatch, that involves devices of the same chip, and global variation, that involves devices on different silicon wafers. For example in scaled technologies the local mismatch can reach 40% in resistors and the variation among different wafers can cause a great difference in circuit working speed and power consumption.

It is possible to partially simulate process variability using Montecarlo simulations on the device parameters. Silicon foundries gives the models of the typical-case and worst-case corner that permit to simulate the parameters variability due to global mismatch.

#### 2.2.2 Interconnection capacitances

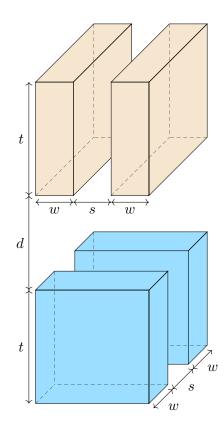

Interconnections scaling is not optimal as for transistors. To provide a good connectivity the number of metal layers increases at every technology node exploiting more and more the vertical dimension, as Figure 1.3 shows. Furthermore at every technology node, to increase the metal routing density, the metals become thicker to maintain the needed cross-section area and prevent electromigration. For this reasons, as Figure 2.6 shows, the distance between the metals of the same layer, s, is smaller than the distance between metals of different layers, d. Furthermore the thickness of the metals, t, is almost the double of its minimum width w.

The dielectric used to fill the spaces between the metals is the same, so the parasitic capacitance between metals of the same layer can be more than double

Figure 2.4: Gate-last fabrication process.

Figure 2.5: Drawing of a 28 nm transistor, showing the dummy gates.

Figure 2.6: In scaled technologies d is more than two times s, and  $t \approx 2w$ . For this reason the parasitic capacitances due to same metal layer are bigger than capacitance due to superposition of different metal layers.

than the capacitance between different metal layers.

### 2.2.3 Digital Switching Noise

CMOS scaling leads to an exponential growth in device number, complexity and speed. This can cause unwanted interactions. Indeed in mixed signal Systemon-Chip the switching of the digital circuits can influence the analog parts of the chip. The noise generated by digital switching activity propagates through parasitic elements due to interconnections and substrate affecting the system performance [49, 50, 51].

AM chips are massively parallel digital circuits. At each clock rising edge the comparison between stored and input data causes high current spikes. The current consumption produced an IR drop on the supply voltage of the memory; moreover, parasitic inductances and capacitances on the printed circuit board can cause oscillations that sometimes affected the functionality of the chip. This problem is usually

mitigated adding decoupling capacitors to the chip package power pins [52]. For the AM09 chip we propose also a complementary approach based on spreading the current peak providing eight clocks with slightly different phases using a Phase Locked Loop (PLL) based on a Digitally Controlled Oscillator (DCO), as explained in Section 3.6.

## Chapter 3

## **Associative Memory ICs**

By starting from late 80s [13], Associative Memories (AMs) was designed for High Energy Physics (HEP) applications. A common problem in HEP applications (in particular at ATLAS experiment) is the identification of particle tracks [17].

ATLAS experiment at Large Hadron Collider (LHC) in Phase-II, will produce up to 700 GB/s raw tracking data. Since a limited amount of events can be transferred to a storage system of the PC farms (for subsequent off-line processing), it is necessary to use an hardware trigger system to filter the relevant data for the event physics analysis. In addition, the luminosity of the collider will strongly increase in the next future. While in the past the trigger system do not take as input the track reconstruction, in view of the Phase-II upgrade a new system trigger system which performs the track reconstruction is needed. In this way, the system efficiency will reach about 90%.

The capability of performing real-time identification of tracks at LHC leads to a very high background rejection. For example, many overlapping proton-proton collisions can be separated using tracks to reconstruct the primary vertexes. Due to the complex structure of events, the trigger system must base its decision on a few tracks among several tracks.

Track reconstruction is performed by means of complex processors designed to achieves challenging constraints. For the Phase-I of LHC (up to 2020) the processor that the ATLAS community uses for this job is called Fast TracKer (FTK) [53]. FTK is composed by 16384 AMchip (version 6) and can perform 31 Ecomp/bit/s. For the next Phase-II of LHC (up to 2026) the process will by called Hardware for the Track Trigger (HTT). HTT will be composed by 13824 AMchip (version 9) and will can compare bit-wise 0.2 Zcomp/bit/s. The systems elaborate the information in two steps:

1. **pattern recognition:** the hit data coming from eight detector layers (over 12 detector layers) is clustered in low-resolution centroids that can be used for a

bit-wise comparison thanks to the AMs;

2. track refining: the found roads (output of the AMs) merged with the data coming from the whole 12 detector layers are used to refine the trajectories of the particles by mean of the  $\tilde{\chi}^2$  calculation.

The AM chip performs the first task exploiting parallelism to the maximum level.

Theoretically, CPUs could provide the expected results (in terms of efficiency and resolution) but they require very large computing power and costs to keep up with the event rate of 250 MHz and the increase of luminosity (up to  $2 \times 10^{35} \text{ cm}^{-2} \text{ s}^{-1}$ ) of Phase II upgrade [54], which will result in more than 400 overlapping protonproton collisions in the same time-bin of the detector clock which identifies an event. Due to the event complexity increase and to the huge amount of data, CPU's tracking capability (with a reasonable number of CPUs per system) will not be sufficient to perform these tasks in future very-high luminosity runs. Trivially, if we consider to use one flop operation to run four word bit-wise comparison, even the most powerful supercomputer existing in the world (called IBM Summit) should not be able to run this analysis. IBM Summit capability is 122.3 Pflops/s. The HTT capability is 0.2 Zcomp/bit/s (2.7 Ecomp/word/s – 22.3x factor). However, the HTT is a specific supercomputer able to run just only bit-wise comparison.

Currently, a dedicate system based on AM is the unique solution that can match all the power, cost, and performance constraints [55].

The AM is a Application specific integrated circuit (ASIC) for pattern recognition based on a smart (CAM) architecture because the chip can store partial matches as they are found and use these partial matches to find correlations among data received at different times (each input bus is independent). In an AM each pattern is stored in a single memory location, like in the commercial CAMs, but the total number of available bits can be organized in N independent words of M bits each. Each word refers to a particular item to be identified in a flux of data that is distributed to one or to a group of multiple words that occupy a particular position in the pattern.

AM has be successfully used for other applications such as image processing [56, 57] and genome sequencing [58].

During my P.h.D. I had the opportunity to work on the design of AM. For this task, I had the responsibility to coordinate the group of Full Custom (FC) blocks. In particular, I am the main designer of CAM cells, and some other important full custom blocks (i.e., quorum). With my contribution the future AMchip (AM08 and AM09) can met the power budget.

20

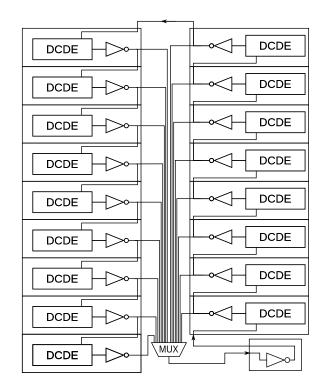

Figure 3.1: Simplified block diagram of the general architecture of the AM chips.

## 3.1 AM chip road-map

The silicon area for the AM06 [59] and the AM09 (the chips that we designed for a large volume production) is  $154 \text{ mm}^2$ . Such large chips costs few millions of dollars, for this reason in the road-map there are two smaller chips to test the circuits and the features of the bigger chip. The large chip is designed mainly for HEP applications, but the smaller test chip provides features that can be used for multidisciplinary applications.

After the successfully project (AM06) for the Phase-1 at LHC, the prototype chips (AM07 and AM08) have an area of  $10 \,\mathrm{mm^2}$  and they contain  $16 \times 1024$  patterns. The production chips (AM09) have an area of  $154 \,\mathrm{mm^2}$  and it contain  $384 \times 1024$  patterns.

Smaller chips can be produced using a Multi Project Wafer (MPW) service to reduce costs, while big-area chips have to be produced using a Multi Layer Mask (MLM) service still to reduce costs. Therefore MLM is recommended for projects that require low or medium production volume. In our case we have to produce about 20 kchips.

Figure 3.2: 64 pattern base memory block.

That is follow now is the time schedule and the aims of each prototype or chip:

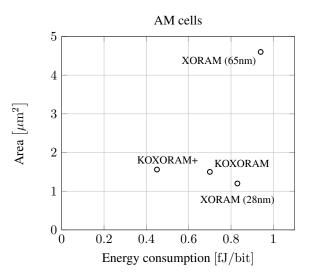

- AM07 prototype: submitted in December 2016. It contains two different types of AM cells: KOXORAM and DOXORAM (an improved version of XORAM [60]). The goal of this test-chip was to test the memory cells and find which one consumes less power. The measurement confirmed the simulations and KOXORAM is proven to be the less consuming cell among the two. Designed in High Power Low-leakage (HPL) 28 nm technology.

- AM08 prototype: will be submitted in May 2019. It will be used to characterize, the new technology, the FC blocks (i.e, quorum, KOXORAM+ cell), the I/O circuits and protocols. This chip must have the same functionality of the AM09 ASIC, but smaller memory size; It will be designed in High Power and Computing (HPC) 28 nm technology.

- **AM09pre pre-production**: full area ASIC to be fabricated with a full-mask set or MLM pilot run. Production corner wafers will be created; It will be designed in HPC 28 nm technology.

- **AM09 production**: full area ASIC with refinements for the mass production. It will be designed in HPC 28 nm technology.

The AM09-pre and the AM09 chips will be developed on the AM08 extending the memory area, therefore the specifications of AM08 versions must be compatible with the specifications of AM09.

Figure 3.3: Write mode operation in AM08

## 3.2 AM chip architecture and functionality

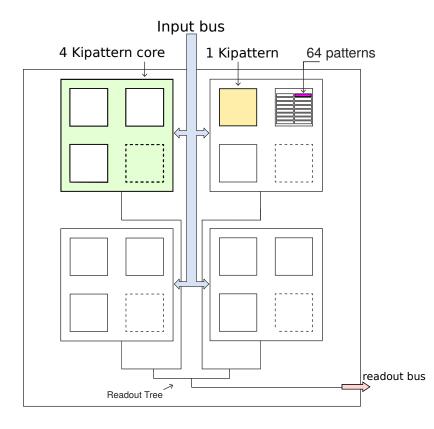

The future AM will be designed with a core approach. AM08 will be composed by 4 elementary core. AM09 will be composed by 96 elementary core. Each core will contains  $4 \times 1024$  patterns. Figure 3.1 shows the simplified block diagram of the general architecture of the AM08 chips.

More details can be found in [28].

The memory inside AM chips is composed by repeating multiple times a 64 patterns elementary block.

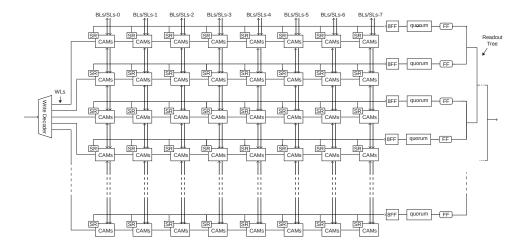

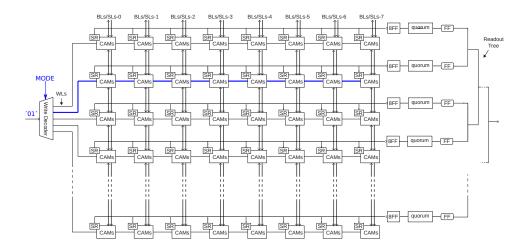

Figure 3.2 shows the functional diagram of 64-rows base block. The memory matrix consist of 64 patterns. Each line contains a *pattern*, that is composed by eight CAMs blocks. Each CAM block consists of a 18 bit *word* (each bit correspond to a CAM cell), and a Set Reset (SR) latch.

#### Write mode

The contents of the pre-defined pattern bank are propagated through the BLs. The address corresponding to a row of the CAM array are fed thanks to the write decoder that generate a one-hot signal for the WL bus (Figure 3.3). When the selected Write Line (WL) corresponding to the designated address is turned on, the pattern is written in the CAM segments at the selected address.

#### **Compare mode**

The information of hits coming from the detector is compared in parallel with the 18 bit word stored in each CAM block. The information is compared in parallel bus

by bus and row by row. If a 18-bit word find a bit-wise correspondence a SR latch is set to high logic value.

For each row, the word of matches (the eight correpondences found) is registered in eight Delay Flip-Flops (D-FFs) or High-Enable Latches located at the input of the quorum circuit using a dedicated pulse (READ\_EV). Normally, this pulse is asserted when all the hits information has been fed into the AM. The pattern-match signal is calculated inside the quorum logic considering the number of matching words and other control signals such as the required matching threshold.

The pattern match outputs are read out with the readout clock and fed to the Road Out Tree (ROT) based on the Fischer's Tree [61]). The ROT reads out addresses of matched patterns as well as encoded 8-bit information of matched word (so called HITMAP) according to a priority embedded in the internal combinational logic. Several hierarchical level of ROT with different input bits are used in the AM to collect all the results.

Once an address/row is read out, the ROT generate a feed-back signal able to assert a DFF located at the output of the quorum. If the output of this DFF is '1' the match output will be disabled. With this strategy, the ROT can proceed to the next elaboration step.

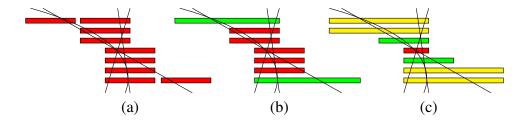

## 3.2.1 Variable resolution

The AM can benefit of this nice feature called variable resolution: A large AM cell bank stores all patterns of interest, for a given input resolution. The AM extracts pattern addresses, when a sufficiently high number of words have matched the incoming data. For most practical problems the set of all patterns with full resolution is extremely large. The AM approach consists in performing pattern matching at reduced resolution first, with a resolution adequate to simplify and reduce the amount of data, and then refining the match inside a Field Programmable Gate Array (FPGA).

A don't care (DC) bit is used to increase the pattern recognition efficiency at different resolutions. It is possible to use patterns of variable shape. As a result of variable resolution, the number of fakes and the bank size decrease, and the efficiency remains high. Hence, for a given efficiency, the number of patterns required will decrease and a smaller pattern bank leads to a lower power consumption.

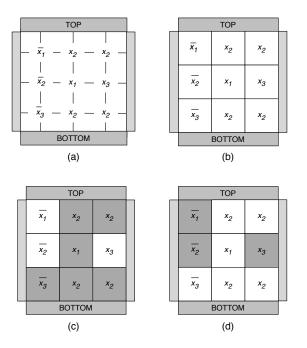

Figure 3.4 shows a qualitative example of the detection of four different particle trajectories. For a given efficiency, the fixed resolution approach requires to store three patterns, while with 1 or 2 DC bit it is necessary to store a single pattern. In addition, for the 2 DC case it is possible to further improve the tracking efficiency. Simulations demonstrated that an AM system with one single DC can be as effective as a three times larger AM system with fixed resolution [62].

Figure 3.4: Diagram illustrating the multi-bit implementation of variable resolution words. Red rectangles are words without DC, green rectangles are words with one DC, yellow rectangles are words with two DC. (a) shows fixed resolution words. (b) shows words with 1 DC-bit. (c) shows words with 2-bit variable resolution, the pixels in this diagram have different scale with respect to the others.

Figure 3.5: Structure of an associative memory

## 3.2.2 AM chip required specifications

The AM chip CAM related specifications and required features are listed in Appendix A, more detailed specifications can be found in [28].

## 3.3 KOXORAM Associative Memory Cell for AM07

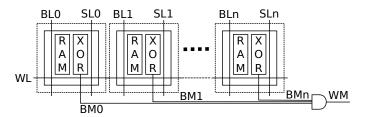

The Figure 3.5 shows the conventional structure of a conventional CAM block. The elementary cell has the capability to store one bit of information (in "write" mode, when the WL signal is high, each cell stores the bit fed on the BLs), and to compare the memory content with the input data (in "compare" mode the RAM contents is compared with the bit at the SL input), providing at the output one bit which indicates whether the input bit is equal to the stored bit (the "bit match" signal BM). When all the bits in a stored word match the input data, then a "word match" signal (WM) is produced at the output.

Since the bit-wise comparison operation can be performed with an XOR logic gate, we have invented in the past a cell called "Xo(R)aM", which is made of a 6T SRAM cell and a pass-transistor XOR gate [60].

The new chip for the future upgrade of the ATLAS experiment will take advantage of the scaled features of the 28 nm CMOS technology, to integrate more devices in the same silicon area [31]. The next generation associative memory chip is expected to contain about 1.5 billion transistors. However, the increased interconnection density in scaled technologies leads to higher parasitic capacitances, which may become the major source of dynamic power dissipation. To overcome this limitation, in the new design we adopted two complementary approaches.

- 1. The new associative memory cell must have a reduced switching activity, i.e., it may be disabled when its output is not relevant for the word matching.

- 2. The input signals must be fed through lines with low parasitic capacitances.

The two design aspects will be discussed in the following subsections.

A first approach to limit the power consumption is based on the reduction of switching activity of the internal nodes. Since the "word match" signal is active only when all the bits in a word are matching, it is obvious that a single non-matching bit will produce a non-matching output; in this case, all the cells operating on subsequent bits can be disabled to save power.

Cells can be disabled by propagating a "kill" signal. When a cell receives a positive "kill" signal from the previous one, it does not perform any comparison and it just propagates the "kill" signal to the next cell. If the input "kill" signal is not active, then the previous bits matched, and the cell compares the input data with the stored bit; if they do not match, the cell generates a positive "kill" signal at the output. Thus, the word matching occurs when the last cell is not providing a positive "kill" signal at its output.

This cell is called KOXORAM (Kill-Out XORAM), because it either performs an XOR logic operation or propagated the "kill" signal at the output, depending of the results of previous cells.

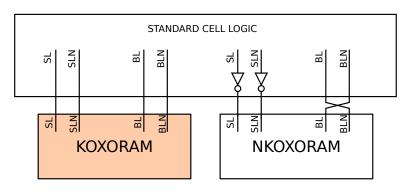

Since in fully CMOS technology the logic cells are inverting, we have designed two cells: one with positive "kill" at the input (NKill\_In) and negative "kill" at the output (Kill\_Out), and the other with negative "kill" at the input (Kill\_In) and positive "kill" at the output (NKill\_Out). The two versions of the cells can be cascaded, as shown in Figure 3.6. To limit the delay introduced by the propagation of the "kill" signal, in our design we have split the 18 bit word into two parts, each containing 9 bits; if the contents of both parts are matching the input data, the two

Figure 3.6: Connection of KOXORAM cells operating on the bits of a word

Kill\_Out signals are 0, and a NOR gate provides the matching signal at the output (Figure 3.6).

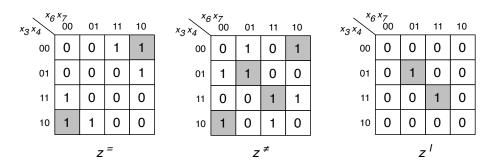

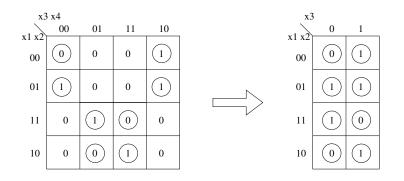

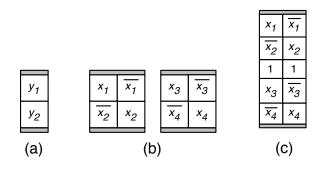

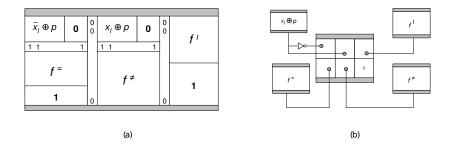

Tables 3.1 and 3.2 show the Karnaugh's maps of the two cells (KOXORAM and NKOXORAM).

| NR:11 C  | (SL, A) |    |    |    |   |

|----------|---------|----|----|----|---|

| NKill_C  | 00      | 01 | 11 | 10 |   |

| Kill In  | 0       | 1  | 1  | 1  | 1 |

| KIII_III | 1       | 0  | 1  | 0  | 1 |

Table 3.1: Karnaugh map of the NKOXORAM cell

Table 3.2: Karnaugh map of the KOXORAM cell

| Kill Ou  | (SL, A) |    |    |    |   |

|----------|---------|----|----|----|---|

| KIII_Ou  | 00      | 01 | 11 | 10 |   |

| NKill In | 0       | 1  | 0  | 1  | 0 |

|          | 1       | 0  | 0  | 0  | 0 |

The dynamic power due to switching activity is the major source of power consumption. Therefore, a special care has been adopted in the design of interconnections for input data.

First of all, different input lines are used: BLs carry the input data to be written into the memory during the writing. SLs propagate the data coming from the input bus to be compared with the data stored inside the CAM. In this way, the search lines are not affected by the parasitic capacitances of the BLs and the switches controlled by write lines (WL). Moreover, the SL signals are routed at a larger distance each other, and they are sufficiently spaced from other signals in the same metal layer, to reduce their capacitance.

BLs and WLs are much less critical, because the memory is written only at the beginning of the operation.

Finally, the aspect ratio of memory cells is chosen in such a way to reduce the cell height. As SLs are propagated vertically, height reduction helps in reducing interconnection capacitance. To reduce further the length of SLs, two cells are merged together. The same contact in the SL is used to drive the signal to four MOS gates (two gates for the MOS transistors in line 0, and two gates for the MOS transistors in line 1).

#### **3.3.1** Schematic Diagrams and Layout

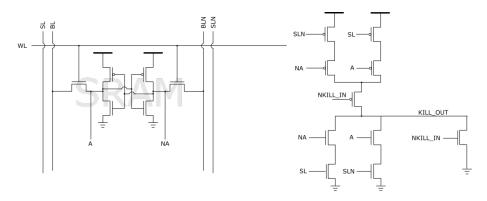

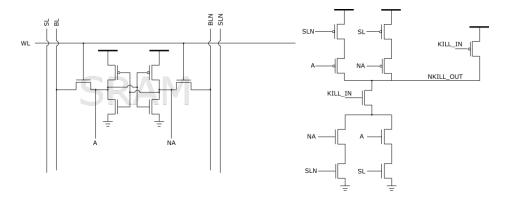

Figures 3.7 and 3.8 illustrate the schematic diagrams of the KOXORAM and of the NKOXORAM cells, respectively.

Figure 3.9 shows the layout of four neighboring cells. The cell height is  $0.91 \,\mu\text{m}$ , and the width is  $6.24 \,\mu\text{m}$  ( $3.12 \,\mu\text{m}$  for each block of two cells).

The total decoupled capacitance associated to the SLs is 0.27 fF for two cells (0.2 fF due to gate capacitances, and 0.07 fF due to metal-metal capacitances).

### 3.3.2 KOXORAM cell working modes

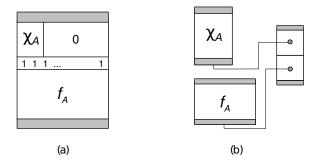

The CAM cells have three different modes, as described in Table 3.3:

- compare, it is used during compare procedure;

- always match, it is used to implement the variable resolution;

- **never match**, it is used to guarantee the setup and hold timings and during test procedures

In the KOXORAM cell this working modes are given by the synthesized logic function. In NKOXORAM cell it is necessary to modify the input connections inverting the SL and SLN signals and memorizing an inverted data swapping the BL with the BLN signal, as shown in Figure 3.10.

#### **3.3.3** Clockless logic

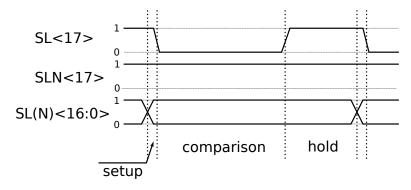

The CAM cell comparison procedure is completely clockless and without an enable signal. The setup and hold times are guarantee using the never-match working mode on one CAM cell as described in Figure 3.11. Precisely, during the setup and hold times the SL<17> and SLN<17> signals are fixed to '1' to prevent the kill signal propagation, and so the final matching, instead during comparison the value of all SLs and SLNs correspond to the input values coming from the detector.

Table 3.3: (N)KOXORAM cell working modes and signals at the interface between the CAM memory block and the standard cells logic

| Working mode        | А   | SL  | SLN | Kill_Out | NKill_Out |

|---------------------|-----|-----|-----|----------|-----------|

| compare (match)     | 1/0 | 1/0 | 0/1 | 0        | 1         |

| compare (not match) | 0/1 | 1/0 | 0/1 | 1        | 0         |

| don't care          | _   | 1   | 1   | 0        | 1         |

| never match         | _   | 0   | 0   | 1        | 0         |

Figure 3.7: Schematic diagram of the KOXORAM cell

Figure 3.8: Schematic diagram of the NKOXORAM cell

Figure 3.9: Layout of four cells, arranged in two groups, to reduce interconnection capacitances of search lines (SL/SLN)

Figure 3.10: Connection scheme between standard cells logic and (N)KOXORAM CAM cells.

### 3.3.4 Simulations

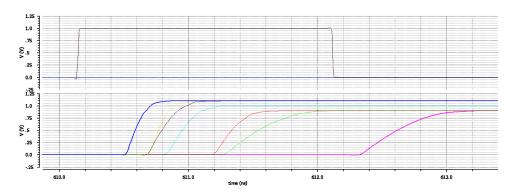

The KOXORAM cell has been extensively simulated to evaluate its performance before fabrication. Interconnection parasitics have been extracted and used for simulation in worst-case corners. The cell has been simulated with a nominal supply voltage  $V_{\text{DD}} = 1 \text{ V}$ , and input data rate f = 200 MHz.

Simulation results demonstrate that in an 18-bit CAM made with the new cell the match signal is asserted to the output with a typical delay of 0.9 ns. The maximum delay, in the slow-slow corner, is 2.5 ns which is less than the input signal period (5 ns). Figure 3.12 shows the delay of the matching signal at the output, in all the worst-case corners.

The average energy is 0.69 fJ/bit, which is a figure lower than the consumption of other designs in the technical literature (e.g., [63]).

The lower power consumption is due to the reduction of both the switching activity of cells and the search line capacitances.

### 3.3.5 Measurements

The AM07 has been fabricated and tested [31]. The chip is fully functional and operates up to 200 MHz. In order to measure the power consumption of cell arrays, input data has been stimulated with a simple dynamic sequence. Input words change between non-matching data ( $0 \times 000000$ ) and matching data ( $0 \times 1ABE0$ ). 500 rows of the memory bank have been written with  $0 \times 1ABE0$ , and 3596 rows with ( $0 \times 3FFFF$ ).

Baseline current consumption has been measured with constant input (i.e., without switching activity on input data except for the SL<17>s). Current and energy consumption are measured by enabling one memory bank at a time (4 × 1024 patterns of 8 words each) with a switching activity equal to 0.5, i.e., when one half of the input bits are changing their value with respect to the data in the previous clock period;  $\Delta$  is defined as the difference between the measurement with switching activity and the baseline measurement. Results of a measurement of 53 chips at 184.32 MHz are summarized in Table 3.4. It is worth remarking that we found a good agreement between measurements and simulation results (within ± 10%).

Table 3.4: Current/energy consumption, measure done on 53 AM07.

|                                        | Currer               | nt [A]              | # bits involved | average energy | sim Calibre |      |

|----------------------------------------|----------------------|---------------------|-----------------|----------------|-------------|------|

|                                        | Mean                 | STD dev.            | # bits involved | [fJ/bit]       | [fJ/bit]    | %    |

| Baseline                               | $3.80 \cdot 10^{-2}$ | $8 \cdot 10^{-4}$   | 524288          |                |             |      |

| Activity on 1/8 input buses            | $4.70 \cdot 10^{-2}$ | $1.3 \cdot 10^{-3}$ | 524288          |                |             |      |

| $\Delta$ (Activity on 1/8 input buses) | $9.04 \cdot 10^{-3}$ | $7.3 \cdot 10^{-4}$ | 65536           | 0.748          | 0.69        | 108% |

30

Figure 3.11: Compare timings of a KOXORAM CAM cell.

Figure 3.12: Simulation result of an 18-bit CAM cell in different corners. Propagation delays at the end of the chain are: 0.9 ns in typical case (cyan), 0.5 ns in fast-fast corner (blue), and 2.5 ns in slow-slow corner (pink).

### **3.4 Improvements for AM08**

Although the AM07 test shows good results, some design aspects have to be improved for AM08 and AM09. The standard cell logic occupies a lot of silicon area and the routing is very dense, it will become even more complicated in future AM chip.

The quorum circuit is the standard cell logic circuit that occupies more area, hence we redesign it with a full custom approach to reduce area occupation and routing complexity.

To reduce the power consumption peak due to parallel propagation of data inside SLs [52] we design a digital PLL that gives eight different clock with different phases at the eight chip cores.

SRAM cells presents metastability issues, so the SRAM cells has been modified to avoid it.

### 3.4.1 Hi performance technology

AM07 is fabricated using the low power version of the 28 nm technology. A low power technology has a low leakage current to reduce power consumption during standby. For this reason it is great for battery powered devices, that stays for a lot of time in standby mode. The drawback is that transistors can output less current than in high-performance technologies. Hence it is necessary to add more buffer along signal paths, the fan-out of a logic gate is lower and the maximum length of interconnection lines is shorter.

The high performance version of the technology is oriented to devices that are not powered with batteries and have to perform heavy computing operations.

We choose the High performance technology for AM08 because being faster it permits to reach the aggressive goals. Moreover the improvement due to optimization of routing, fan-out and signal paths will permit us to reach a power consumption similar to low power technology.

### 3.4.2 KOXORAM+

To reach the specification target of 400 MHz in typical case it is necessary to change the architecture of the memory row. Due to the limited number of metal layers for routing and the propagation speed of the technology used in AM07 the chain that has a maximum of nine KOXORAM cell in series.

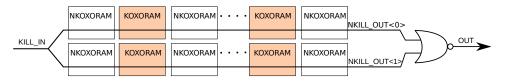

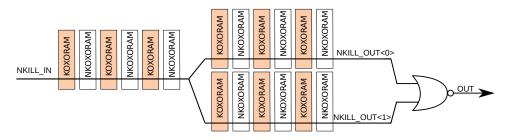

The new technology is faster and provides more metal layers suitable for routing, thus in AM08 the row has a series of 12 KOXORAM cell, as shown in Figure 3.13. This architecture is also less power consuming: the power used to propagate the data in SLs is the same, but less power is used to propagate the kill signal. The probability of cell matching can be approximated to 50%. Being  $P_{Kill}$  the power needed to propagate the kill signal, the architecture in Figure 3.6 consumes  $2\sum_{n=1}^{9} P_{Kill}/2^n \approx 2P_{Kill}$  and the architecture in Figure 3.13 consumes  $\sum_{n=1}^{6} P_{Kill}/2^n + 2\sum_{n=7}^{12} P_{Kill}/2^n \approx P_{Kill}$ .

Simulation with back-annotated netlist shows an energy consumption of 0.42 fJ/bit, approximately 30% less than the former KOXORAM memory. KOXORAM+ fulfills the speed requirements of 400 MHz in typical and fast case and 250 MHz in slow. Table 3.5 shows the minimum timings in each simulation corner.

### 3.4.3 SRAM metastability

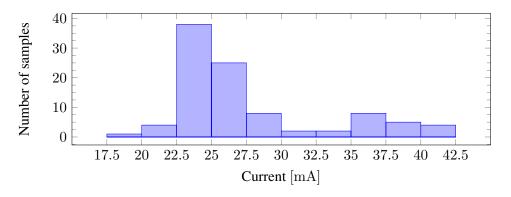

AM07 tests shows that the current consumption at startup is higher than after writing the CAM SRAM memories. The current at startup is  $27 \pm 6$  mA and after the writing is 4.40(0.01) mA per  $16 \times 1024$  patterns, Figure 3.14 shows the distribution of the 100 current measurements at startup of a single chip. This behavour is typical of SRAM memories that present metastability. Indeed if the output and the input of an inverter are at the same voltage there is a unstable equilibrium point, an SRAM in that working point consumes a lot more power than SRAM with definite states.

The AM09 chip will contain  $3 \times 128$ Ki patterns, and the power consumption at startup due to metastability would be  $\approx 0.5$  A. To reduce the number of metastable SRAM we design an asymmetric SRAM cell.

#### **Butterfly diagram**

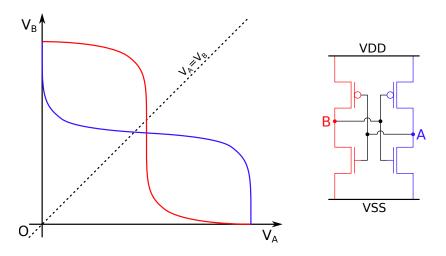

Butterfly diagrams are commonly used to study the properties and the metastability of an SRAM [64, 65, 66].

An example of butterfly diagram is shown in Figure 3.15. The butterfly diagram is drawn plotting the two characteristics of the SRAM inverters on the same graph. It is possible to extract a lot of information from this diagram, but we focus our attention on metastability.

An SRAM is metastable when the crossing point between the two characteristics is placed on the bisector of I and III quadrants (where  $V_A = V_B$ ).

Table 3.5: Timings of KOXORAM+ memory

| [ns]    | tt  | SS  | ff  |

|---------|-----|-----|-----|

| setup   | 0.1 | 0.1 | 0.1 |

| compare | 0.8 | 1.7 | 0.5 |

| hold    | 0.4 | 0.9 | 0.2 |

#### SRAM design

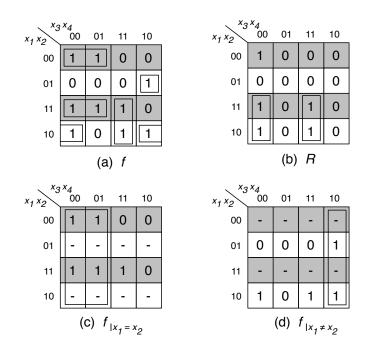

To characterize the SRAM we run a Montecarlo simulation on the space of technology parameters, with 1000 points, and we plot the butterfly diagrams and the crossing points. The results of the Montecarlo simulation are shown in Figure 3.16.

In particular in Figure 3.16a there is the simulation of a completely symmetric SRAM with minimum dimension transistors. The crossing points are placed across the bisector, indicating a non-negligible metastable behavior.

To reduce the number of metastable SRAM cells we unbalance the SRAM enlarging the width of a p-MOS transistor from 100 nm to 360 nm and opposite n-MOS transistor from 100 nm to 180 nm. This modification is done without increasing the area of the KOXORAM cell, as shown in Figure 3.16d, the extra active area helps also to meet the design rule of minimum active area density.

In Figure 3.16b there is the simulation of the asymmetric SRAM, there are less point near the bisector hence metastability will be rarer than in the symmetric configuration. In Figure 3.16c there is a comparison of the distribution of distance of the crossing points between symmetric and asymmetric SRAM. The distribution shows that the asymmetric SRAM has a negligible probability to show a metastable behaviour.

### 3.5 Quorum circuit

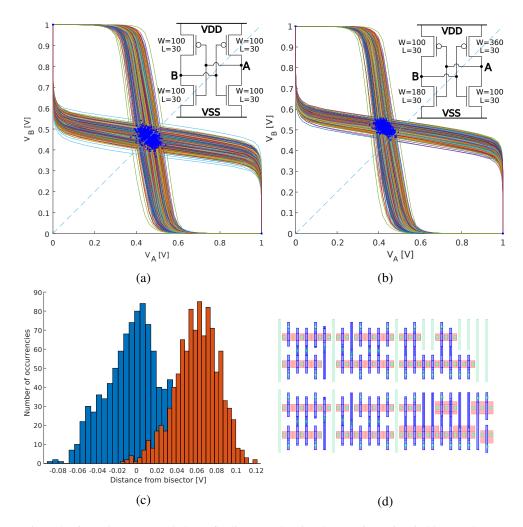

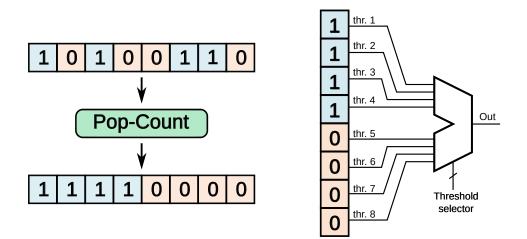

The AM architecture is structured in words of 18 bits. Each word contains the spatial coordinates of a group of neighboring sensor pixels on the same layer of the detector; 8 words (from 8 different detector layers) make a pattern, and every matching between an input word and the stored data triggers a Set-Reset (SR) latch to high-logic value [15]. To perform the trigger operation we need to know how many patterns are matching. An obvious solution consist in counting how many SR latches have been triggered by the input event data. To obtain a good performance, we need to consider all the possible thresholds, from 0 to 8 matches. For this task, a population count circuit is used.

Conventional population count circuits use full adders and half adders. Dalalah et al. [67] propose an 8-bit circuit that employs CMOS logic gates, with 162 transistors in total. Pedroni, in [68] presents an 8 bit sorter composed by 56 logic gates. Despite the literature solutions optimize the transistor number, for 28nm technology is preferable to design a repetitive architecture to minimize the number of interconnections in order to reduce area and dynamic power consumption.

In AM07 chip, the population count circuit is designed by synthesizing a behavioral VHDL code with the Cadence RC software, and it is implemented using the standard-cell library. With this approach, the area occupied by the population

### 34

Figure 3.13: Architecture of a single row of KOXORAM+ cell

Figure 3.14: Histogram of the measurements of current due to SRAM metastability at startup. The histogram shows the distribution of 100 measurements of a single chip.

Figure 3.15: Example of butterfly diagram

Figure 3.16: (a),(b): Montecarlo butterfly diagrams showing the crossing points in blue. At the top right of each diagram there is the schematic of the simulated SRAM cell reporting the width and the length of each MOS transistors (in nm). (c): distribution of the distance of the crossing points from the bisector. The symmetric SRAM is plotted in blue, the asymmetric in red. (d): layout of the KOXORAM cell. On top there is the layout of the symmetric version and on bottom the layout of the asymmetric one.

count circuit is about three times the area of the CAM blocks. The RC compiler reports a total area of  $138 \,\mu m^2$ .

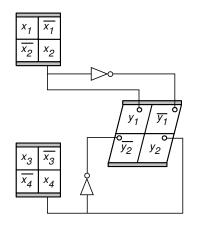

For this reasons it is designed a new full custom circuit, where the single element is based on the *bubble-sort* algorithm and uses a divide-and conquer approach to perform the population count with a combinational logic implemented in fully-CMOS approach. As in the bubble-sort algorithm in software, the circuit swaps the logic values at the inputs to give an ordered set at the output. The outputs are given to the threshold selector (designed using a multiplexer) that selects the output corresponding to the required threshold, as shown in Figure 3.17.

The designed circuit is asynchronous, and it is made of three layers of combinational logic. The output of the proposed circuit passes trough a full custom control logic circuit, as described in [69]. This control logic is composed by:

- A threshold selector that selects the output corresponding to the chosen threshold (Figure 3.17)

- SR latches that receive in input global signals and WL to put the output of the single quorumA circuit to '1' or '0' independently from the inputs (this feature is useful during the test procedure).

- Logic gates that uses global signals to put the output of the all quorum circuit of a 64 word memory block to '1' or '0' independently from the inputs (this feature is useful during the test procedure)

- an SR latch that stores the read flag signals that comes from the readout tree and indicates if the readout procedure was already made.

The envisaged solution employs more transistors than the circuit proposed in [69], but it leads to a more compact layout design, which occupies a smaller silicon area.

The bubble-sort circuit exhibits also a better power consumption: as it is an asynchronous circuit, it has less switching activity with respect to a synchronous circuit.

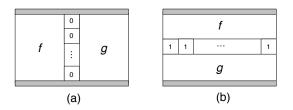

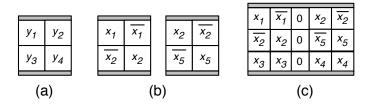

The circuit goal is to obtain the number of zeros (or ones) within an 8-bit bus. The positions of zeros are not a-priori predictable. As for the bubble-sort algorithm, the idea consists in sorting the zeros and the ones (to separate them), and in finding the position of the transition from 0 to 1 in the sorted array. To achieve this result, we employ a combinational logic which shifts the ones towards the Most Significant Bit (MSB) position of the output bus and the zeros towards the Least Significant Bit (LSB) position.

In 28 nm technologies, the on-resistance of MOS transistors is too high to allow a design with eight transistors connected in series. For this reason, it is not possible

Figure 3.17: The Pop-Count circuit swaps the logic values at the inputs and gives an ordered set at the output. The output are then processed with a Threshold Selector, that selects the output corresponding to the wanted threshold.

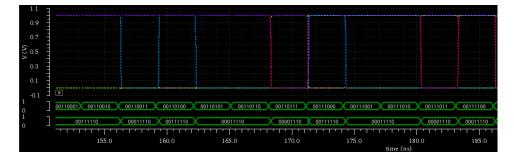

Figure 3.18: Top waveforms: analog signals; middle waveform: input bus; bottom waveform: output bus. The zeros are shifted to the MSB positions, and the ones to the LSB positions

to design a logic with 8 input/output bits, because its timing and functionality will be degraded. Therefore, we limit the number of transistors in series to four.

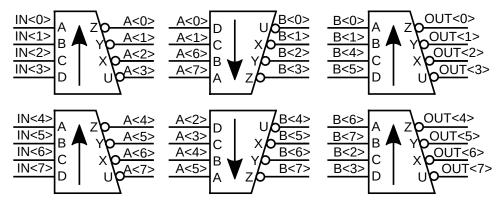

The overall circuit is obtained by using two sets of three cascaded 4-bit bubblesorter circuits (Figure 3.19) and by scrambling some wires. A cascade of three stages is needed to guarantee the complete sorting for all input bit configurations.

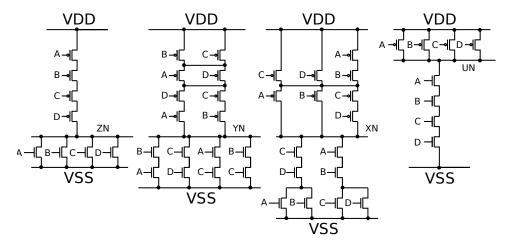

The boolean expressions for the elementary cells are:

$$\overline{Z} = A + B + C + D \tag{3.1}$$

$$\overline{\mathbf{Y}} = (\mathbf{A} + \mathbf{D}) \cdot (\mathbf{B} + \mathbf{C}) + \mathbf{A} \cdot \mathbf{D} + \mathbf{B} \cdot \mathbf{C}$$

(3.2)

$$\overline{\mathbf{X}} = \mathbf{C} \cdot \mathbf{D} \cdot (\mathbf{A} + \mathbf{B}) + \mathbf{A} \cdot \mathbf{B} \cdot (\mathbf{C} + \mathbf{D})$$

(3.3)

$$\overline{\mathbf{U}} = \mathbf{A} \cdot \mathbf{B} \cdot \mathbf{C} \cdot \mathbf{D} \tag{3.4}$$

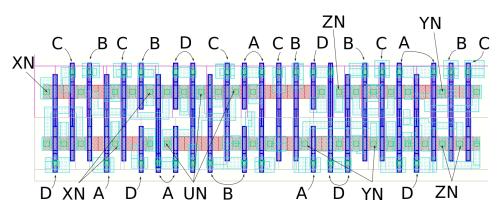

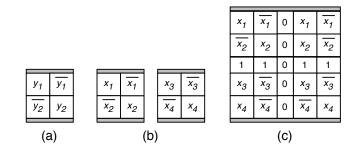

The logic generates inverted signals at the output. From the four boolean expressions (3.1–3.4), we derived a fully-CMOS circuit made of stacked transistors, using the Euler's graph method. Figure 3.20 shows the schematic diagrams of the four parts of each block. The overall circuit is made of 48 transistors. Several transistors are stacked in the layout, in order to save silicon area. Figure 3.21 shows the layout of the elementary cell.

Compared with other solutions, this circuit occupies less silicon area. In fact, the circuit described in the previous work [69] is larger by a factor of 1.17, and a circuit with the same functionality implemented with the foundry standard cell library is larger by a factor of 5.

### 3.5.1 Simulation Results

Simulations have been carried out in different corners. Simulations covered all the possible  $2^8$  input bit combinations. Output results have been checked with a behavioral model to guarantee the full functionality.

Figure 3.19: Schematic diagram of population counter

Figure 3.20: CMOS schematics of the elementary cell. The four sub-circuits implement the four boolean expressions in (3.1)–(3.4), respectively.

Figure 3.21: Layout of the elementary cell. Transistors have been stacked as much as possible, to obtain a very compact design

Results demonstrates the functionality of the circuit at the required speed: 400 MHz. To avoid possible spurious transitions, output data of the control logic has been registered thanks to a conventional delay FF. Figure 3.18 shows a detail of the simulated waveforms. Simulations have been performed with Cadence Analog Mixed Simulator (AMS) and back-annotated via Mentor Graphics Calibre PEX Extractor. The stimuli are generated using the output of a 8-bit counter written in Verilog code.

The circuit consumes 3.75 aJ/bit. The previous full-custom implementation occupies five times the area of the full-custom circuit and contains more transistors and interconnections. In this technology the dynamic power consumption due to charge and discharge of interconnections is not negligible. For this reason we can tell that the power consumption of the full-custom quorum is certainly lower than the standard-cell one.

### 3.5.2 Design Verification

Layout Versus Schematic (LVS) and Design Rule Check (DRC) have been performed and results are clean.

### 3.6 Digitally Controlled Oscillator

AMs are massively parallel circuits. When an AM chip switches from 'idle' mode to 'compare' mode the current rises from zero to several Ampere in about 0.1 ns and current peaks are synchronous with the clock.

This current consumption generates a ripple on the supply voltage of the chip that can affect the correct functionality of the whole device [59].

For this reason AM09 will implement a circuit to reduce this current peak, splitting the single peak in eight smaller peaks.

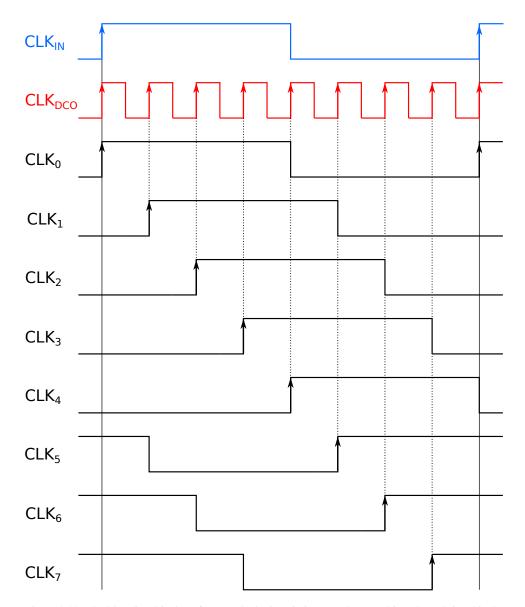

This procedure is done using a PLL circuit that generates an internal clock that is eight times faster than input clock. Then with the PLL clock it is possible to generate eight different clock phases with the same frequency than the input clock, as Figure 3.22 shows.

The PLL is based on a Digitally-Controlled Oscillator driven by a fairly simple state-machine. This circuit solution was chosen instead of typical Voltage-Controlled Oscillators (VCOs). In fact VCO schematics are based on operational amplifiers and passive components. The 28 nm technology is mainly intended for digital circuits and generally do not provide modules for passive components that can be used successfully in the design of analog circuits. Moreover, the value of these analog components suffer from great process variability.

Figure 3.22: The blue signal is the reference clock given in input to the AM chip. The red signal is the clock generated by the PLL. The black signals are the clocks with the same frequency than the input clock, but different phases.

For these reasons the solution adopted is a ring oscillator with full-digital frequency control, in which the analog part of the circuit is minimized and realized only with active devices.

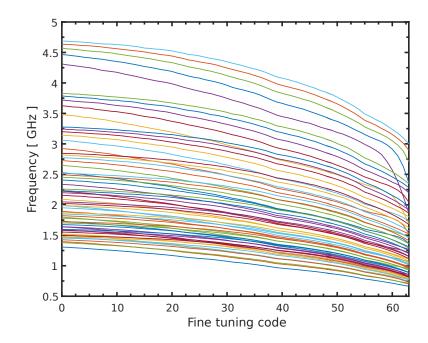

The main requirements for the DCO are: a frequency from 2 GHz to 3.2 GHz, a power consumption of less than 10 mW and a phase noise not exceeding 1/8 of the clock period. Linearity is not required, while monotonicity is a strong requirement.

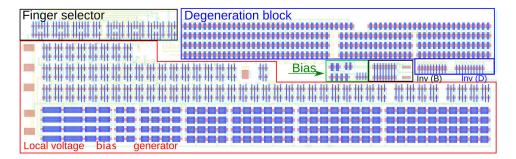

### 3.6.1 Circuit Structure

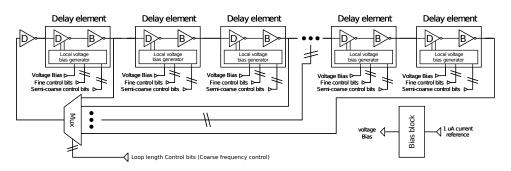

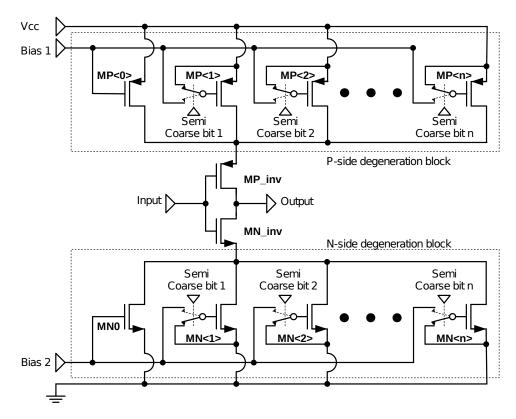

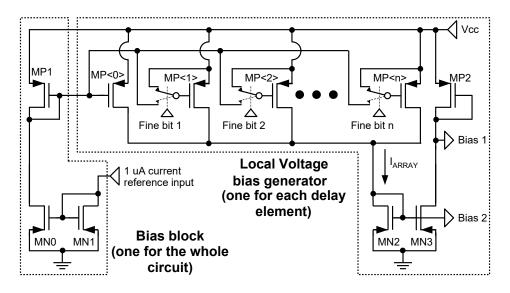

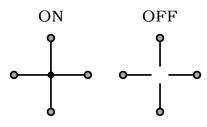

The DCO is based on a ring oscillator with a frequency range from 2 GHz to 3.2 GHz in typical case. The oscillation frequency is tuned by acting on three separate thermometric controls. The first one, namely the "coarse frequency control" (12 bits), selects the length of the delay chain in the ring. The fastest configuration is made of just an inverter and one delay element, while the slowest is made of an inverter and 25 delay elements. The two other frequency controls, the "semi-coarse control" (6 bits) and the "fine control" (63 bits) are used to adjust the delay introduced by each element.

The length of the chain should be adjusted only at power-up because is intended mainly to select between different operating frequencies (e.g., 2 GHz or 3 GHz) and to compensate for frequency variations due to the fabrication process. During operation, frequency and phase tracking is performed only with the "fine" and "semi-coarse" controls. The multiplexer can be used also to activate-deactivate the oscillator and to provide a start-up stimulus to avoid possible equilibrium states. The bias circuit takes a  $1 \,\mu\text{A}$  current reference, turns it into a voltage bias and distributes it to the delay elements. Figure 3.23 shows a block diagram of the ring oscillator.

Each delay element is made of two inverters and a Local Voltage Bias Generator (LVBG).

The first inverter, marked with "D" in Figure 3.23, is the main source of delay,

Figure 3.23: Block diagram of the ring oscillator. For clarity, only 5 delay elements of 25 are shown. The bias block in the bottom-right corner produces a voltage bias used by the delay elements. The multiplexer has 13 inputs (only 4 are shown).

Figure 3.24: Schematic of the first inverter inside the delay element.