## UNIVERSITÁ DEGLI STUDI DI MILANO

Scuola di Dottorato in Fisica, Astrofisica e Fisica Applicata Dipartimento di Fisica

Corso di Dottorato in Fisica, Astrofisica e Fisica Applicata Ciclo XXX

# Demonstrator System for the Phase-I Upgrade of the Trigger Readout Electronics of the ATLAS Liquid Argon Calorimeters at the LHC

Settore Scientifico Disciplinare FIS/01 - FIS/04

Supervisore: Professor Valentino Liberali Co-supervisore: Dottor Francesco Tartarelli

Coordinatore: Professor Francesco RAGUSA

Tesi di Dottorato di: Alessandra Camplani

Anno Accademico 2016/2017

#### Commission of the final examination:

External Referees: Marco Lisboa Leite (Universidade de Sao Paulo) Monica Alderighi (IASF - INAF, Milano)

External Members: Mike Wirthlin (Brigham Young University of Utah) Yuji Enari (University of Tokio)

Internal Member: Massimo Lazzaroni (Università degli Studi di Milano)

#### **Final examination:**

January 19th, 2018

Università degli Studi di Milano, Dipartimento di Fisica, Milano, Italy

To my family.

## Cover illustration:

Geneva Lake - Jet d'eau Max Emde March 19, 2017

## **MIUR subjects:**

FIS/01 FIS/04

## Contents

| In | trodu                                    | iction                                             | v        |  |  |

|----|------------------------------------------|----------------------------------------------------|----------|--|--|

|    | Gen                                      | eral introduction                                  | vii      |  |  |

|    | The                                      | sis introduction                                   | vii      |  |  |

| 1  | Cern and LHC                             |                                                    |          |  |  |

|    | 1.1                                      | CERN                                               | <b>1</b> |  |  |

|    | 1.2                                      | The Large Hadron Collider (LHC)                    | 2        |  |  |

|    |                                          | LHC 2017 achievements and future perspectives      | 4        |  |  |

|    |                                          | LHC plan                                           | 4        |  |  |

|    | 1.5                                      |                                                    | 5        |  |  |

| 2  | ATI                                      | AS                                                 | 7        |  |  |

|    | 2.1                                      | Structure of the ATLAS detector                    | 7        |  |  |

|    | 2.2                                      | Inner Detector                                     | 8        |  |  |

|    | 2.3                                      | Calorimeters                                       | 11       |  |  |

|    | 2.4                                      | Muon system                                        | 12       |  |  |

|    | 2.5                                      | Magnet system                                      | 13       |  |  |

|    | 2.6                                      | Forward detectors                                  | 14       |  |  |

|    | 2.7                                      | Trigger and data acquisition                       | 15       |  |  |

| 3  | Liq                                      | uid Argon Calorimeter                              | 17       |  |  |

|    | 3.1                                      | Introduction                                       | 17       |  |  |

|    | 3.2                                      | Electromagnetic calorimeter                        | 18       |  |  |

|    | 3.3                                      | Hadronic calorimeters                              | 20       |  |  |

|    | 3.4                                      | Structure of ATLAS calorimeters                    | 22       |  |  |

|    | 3.5                                      | LAr ATLAS Calorimeter                              | 23       |  |  |

|    | 3.6                                      | 0 1 0                                              | 26       |  |  |

|    | 3.7                                      | 00 5                                               | 27       |  |  |

|    | 3.8                                      | L1-trigger readout                                 | 30       |  |  |

| 4  | Liquid Argon Calorimeter Phase-I Upgrade |                                                    |          |  |  |

|    | 4.1                                      | Physics requirements and performance               | 31       |  |  |

|    | 4.2                                      | Level-1 trigger performances                       | 34       |  |  |

|    | 4.3                                      | Implementation of the trigger readout system       | 36       |  |  |

|    | 4.4                                      | Towards the ATLAS LAr calorimeter Phase-II upgrade | 42       |  |  |

| 5           | Phas                                                                             | e-I Upgrade Demonstrator                                                                                                                                                                               | 45                                                                               |

|-------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|             | 5.1                                                                              | Demonstrator system                                                                                                                                                                                    | 45                                                                               |

|             | 5.2                                                                              | ABBA firmware                                                                                                                                                                                          | 51                                                                               |

|             | 5.3                                                                              | Validation of the firmware                                                                                                                                                                             | 54                                                                               |

|             | 5.4                                                                              | Physics runs with the demonstrator                                                                                                                                                                     | 59                                                                               |

|             | 5.5                                                                              | Firmware contribution                                                                                                                                                                                  | 64                                                                               |

|             | 5.6                                                                              | I2C-bus project                                                                                                                                                                                        | 64                                                                               |

|             | 5.7                                                                              | Reset structure project                                                                                                                                                                                | 72                                                                               |

|             | 5.8                                                                              | Latency project                                                                                                                                                                                        | 74                                                                               |

|             | 5.9                                                                              | Identification of firmware failures                                                                                                                                                                    | 77                                                                               |

| 6           | Phas                                                                             | e-I Upgrade System Test                                                                                                                                                                                | 83                                                                               |

|             | 6.1                                                                              | The system                                                                                                                                                                                             | 83                                                                               |

|             | 6.2                                                                              | LATOME firmware                                                                                                                                                                                        | 85                                                                               |

|             |                                                                                  | Firmware contribution                                                                                                                                                                                  | 92                                                                               |

|             |                                                                                  | TTC firmware module                                                                                                                                                                                    | 93                                                                               |

|             |                                                                                  | Results from IStage block                                                                                                                                                                              | 111                                                                              |

|             | 6.6                                                                              | Final considerations                                                                                                                                                                                   | 112                                                                              |

|             |                                                                                  |                                                                                                                                                                                                        |                                                                                  |

| 7           | Con                                                                              | clusions                                                                                                                                                                                               | 115                                                                              |

| -           |                                                                                  |                                                                                                                                                                                                        |                                                                                  |

| -           | FPG                                                                              | As and VHDL                                                                                                                                                                                            | 117                                                                              |

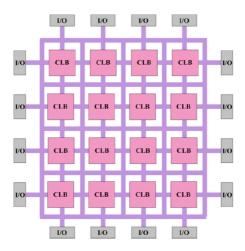

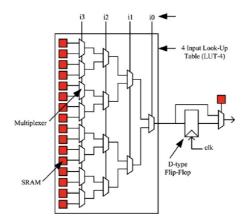

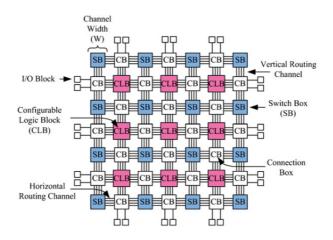

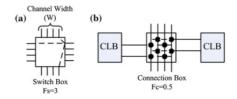

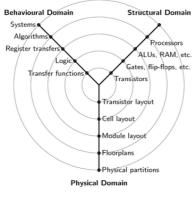

| -           | <b>FPG</b><br>A.1                                                                | <b>As and VHDL</b><br>Field Programmable Gate Array                                                                                                                                                    | <b>117</b><br>117                                                                |

| -           | <b>FPG</b><br>A.1<br>A.2                                                         | As and VHDL                                                                                                                                                                                            | <b>117</b><br>117                                                                |

| A           | <b>FPG</b><br>A.1<br>A.2<br>A.3                                                  | <b>As and VHDL</b><br>Field Programmable Gate Array<br>Very high speed integrated circuits Hardware Description Language (VHDL                                                                         | <b>117</b><br>117<br>.)119<br>122                                                |

| -           | <b>FPG</b><br>A.1<br>A.2<br>A.3<br><b>Git</b>                                    | <b>As and VHDL</b><br>Field Programmable Gate Array<br>Very high speed integrated circuits Hardware Description Language (VHDL<br>Testbench                                                            | <b>117</b><br>117<br>.)119<br>122<br><b>125</b>                                  |

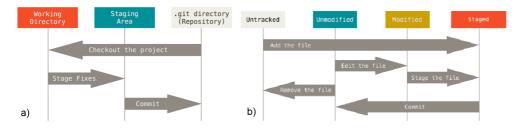

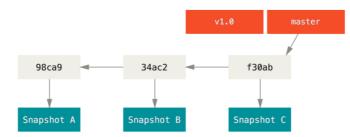

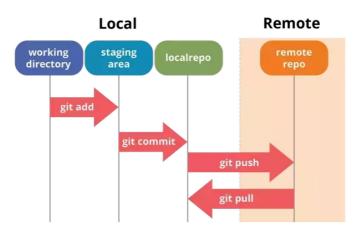

| A           | <b>FPG</b><br>A.1<br>A.2<br>A.3<br><b>Git</b>                                    | <b>As and VHDL</b><br>Field Programmable Gate Array<br>Very high speed integrated circuits Hardware Description Language (VHDL<br>Testbench<br>How it works                                            | <b>117</b><br>117<br>.)119<br>122                                                |

| A<br>B      | FPG<br>A.1<br>A.2<br>A.3<br>Git<br>B.1<br>B.2                                    | As and VHDL<br>Field Programmable Gate Array<br>Very high speed integrated circuits Hardware Description Language (VHDL<br>Testbench<br>How it works<br>LDPS firmware repository                       | <b>117</b><br>117<br>.)119<br>122<br><b>125</b><br>125<br>127                    |

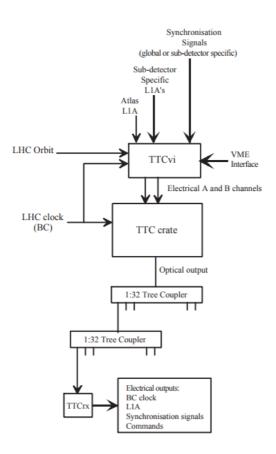

| A<br>B      | FPG<br>A.1<br>A.2<br>A.3<br>Git<br>B.1<br>B.2<br>TTC                             | As and VHDL<br>Field Programmable Gate Array<br>Very high speed integrated circuits Hardware Description Language (VHDL<br>Testbench<br>How it works<br>LDPS firmware repository<br>System             | <b>117</b><br>117<br>.)119<br>122<br><b>125</b><br>125<br>127<br><b>131</b>      |

| A<br>B      | <b>FPG</b><br>A.1<br>A.2<br>A.3<br><b>Git</b><br>B.1<br>B.2<br><b>TTC</b><br>C.1 | As and VHDL<br>Field Programmable Gate Array<br>Very high speed integrated circuits Hardware Description Language (VHDL<br>Testbench<br>How it works<br>LDPS firmware repository<br>System<br>TTC data | <b>117</b><br>117<br>119<br>122<br><b>125</b><br>125<br>127<br><b>131</b><br>131 |

| A<br>B      | <b>FPG</b><br>A.1<br>A.2<br>A.3<br><b>Git</b><br>B.1<br>B.2<br><b>TTC</b><br>C.1 | As and VHDL<br>Field Programmable Gate Array<br>Very high speed integrated circuits Hardware Description Language (VHDL<br>Testbench<br>How it works<br>LDPS firmware repository<br>System             | <b>117</b><br>117<br>.)119<br>122<br><b>125</b><br>125<br>127<br><b>131</b>      |

| A<br>B<br>C | FPG<br>A.1<br>A.2<br>A.3<br>Git<br>B.1<br>B.2<br>TTC<br>C.1<br>C.2               | As and VHDL<br>Field Programmable Gate Array<br>Very high speed integrated circuits Hardware Description Language (VHDL<br>Testbench<br>How it works<br>LDPS firmware repository<br>System<br>TTC data | <b>117</b><br>117<br>119<br>122<br><b>125</b><br>125<br>127<br><b>131</b><br>131 |

## Abstract

#### **General introduction**

I started my Ph.D. at the Physics Department of the Università degli Studi di Milano in November 2014. I carried out my research activity within the ATLAS experiment at the Large Hadron Collider (LHC) at CERN, mainly focusing on the upgrade of the ATLAS Liquid Argon (LAr) electromagnetic calorimeter Phase-I trigger electronics. The main topic of my doctoral project is the implementation of VHDL firmware for the Field Programmable Gate Arrays (FPGAs) of the new calorimeter trigger electronics.

I spent the first of the three Ph.D. years working in Milano and the last two years at CERN, supported by a contract awarded from the ATLAS LAr calorimeter group. During the three years of activity, I contributed to the development and maintenance of the FPGA readout firmware for the LAr Phase-I demonstrator system, set up and installed in the ATLAS detector during summer 2014. The purpose of the system is to validate the energy reconstruction and collect real collision data using a pre-prototype of the future front-end and back-end electronics.

In addition, I joined the group working on the firmware development for the FPGAs of the new Phase-I back-end boards. I was asked to be in charge of the firmware module for decoding the Timing Trigger and Control (TTC) signals coming from the LHC central trigger processor.

#### **Thesis introduction**

This Ph.D. thesis is inserted in the context of the ATLAS experiment at the LHC. The first four chapters are mainly dedicated to give a general overview of the experiment and the system in which this project is inserted.

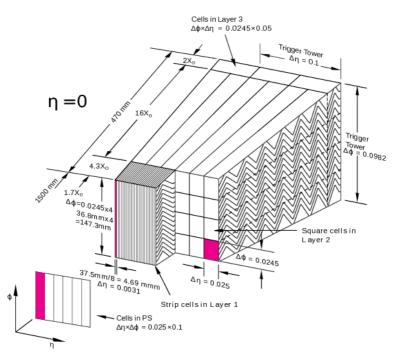

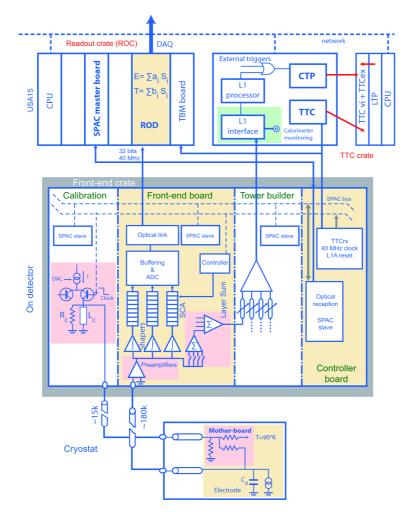

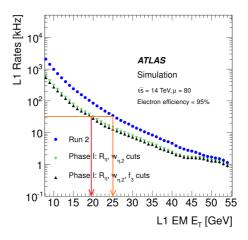

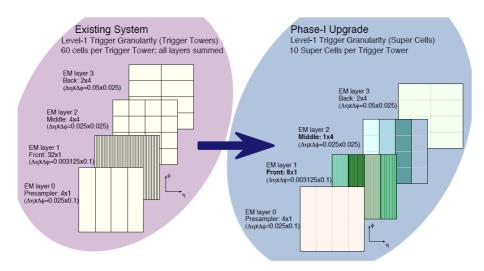

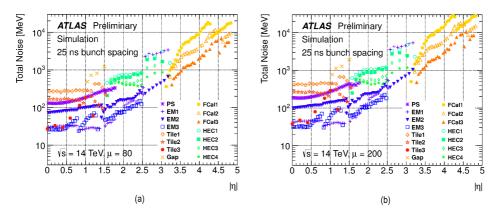

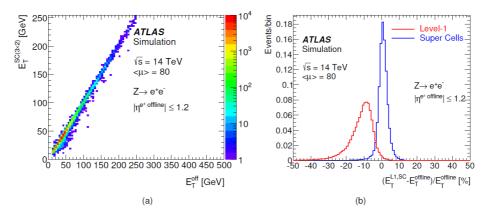

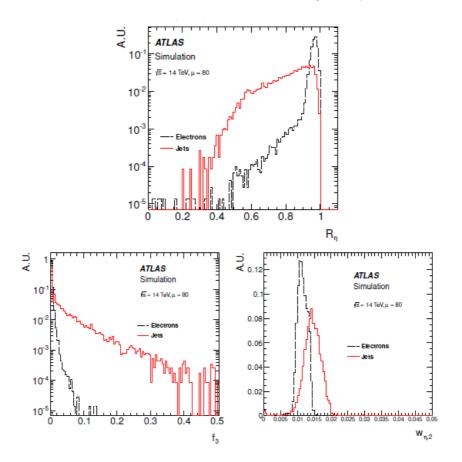

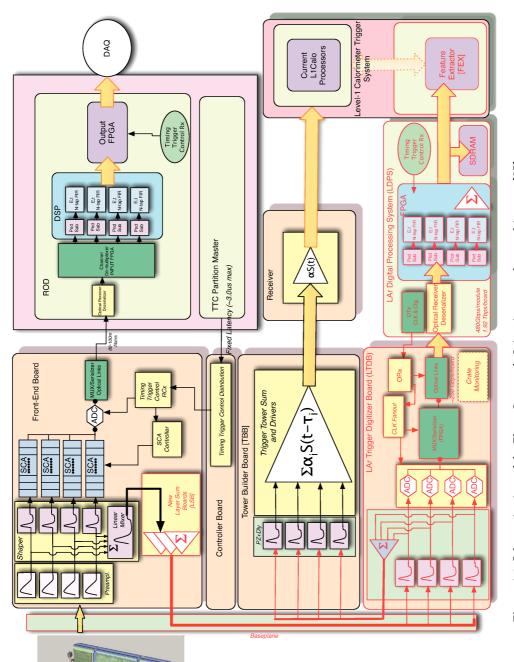

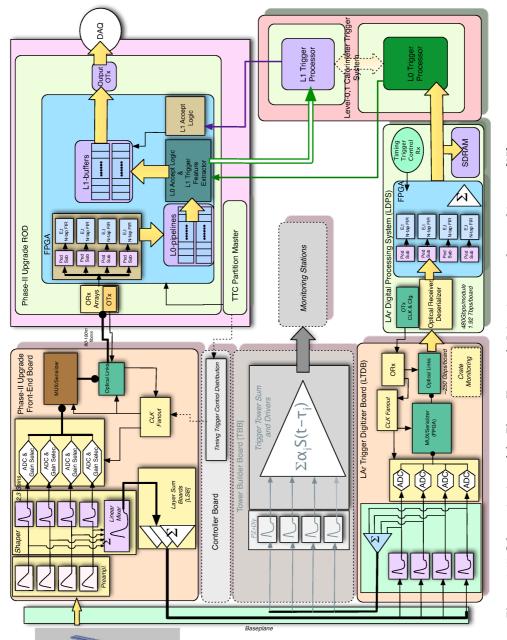

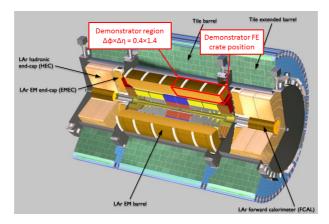

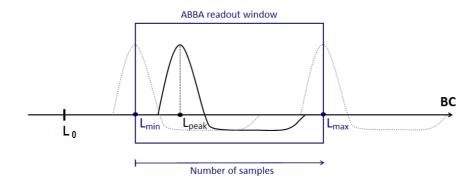

In the coming years, the LHC will undergo a series of upgrades leading to luminosities well beyond the nominal value, with the aim of extending and improving the physics program of its experiments. Meeting this challenge will require significant detector optimizations, changes and improvements. The ATLAS experiment at the LHC is a multi-purpose particle detector with a forward-backward symmetric cylindrical geometry, a fully azimuthal coverage and a rapidity coverage up to 4.9. The purpose of the ATLAS LAr calorimeter upgrade is to provide higher-granularity, higher-resolution and longitudinal shower information from the calorimeter to the Level-1 trigger processors to improve the trigger energy resolution and the event selection efficiency. The existing calorimeter trigger readout is based on "Trigger Towers" which sum the energy deposited along the longitudinal layers in an area of  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1^1$ . The towers will evolve in a new finer scheme, called "Super Cells", which for example in the barrel "middle" sampling (where most of the energy is collected), will have a granularity of  $\Delta \eta \times \Delta \phi = 0.025 \times 0.1$ . In this perspective both LAr front-end and back-end electronics will be improved and extended.

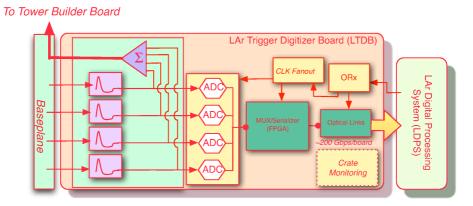

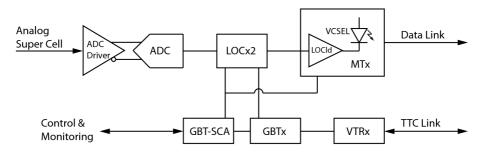

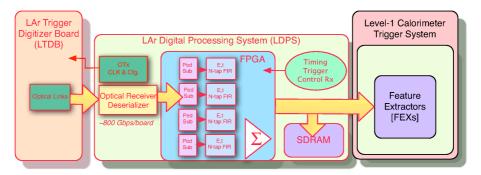

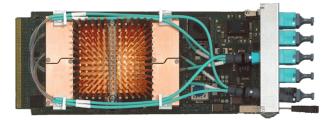

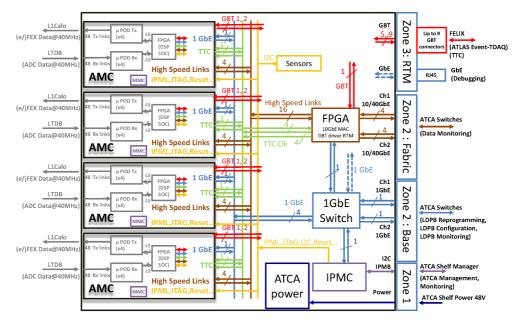

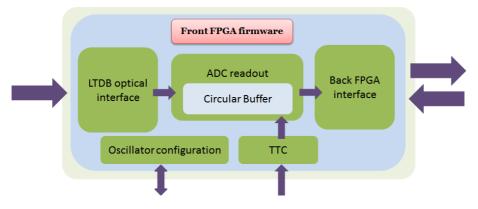

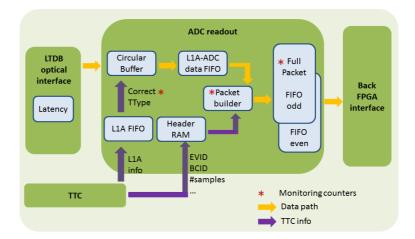

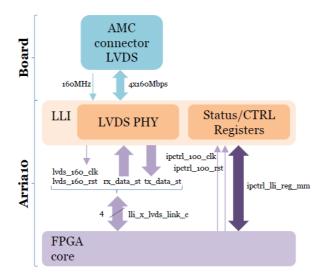

The key electronic board of the upgrade is the LAr Trigger Digitizer Board (LTDB) which will receive, digitize and send to the new back-end electronics the Super Cell signals. The back-end system, called LAr Digital Processing System (LDPS), will reconstruct the transverse energy of each Super Cell and transmit the result to the Level-1 calorimeter trigger system. The LDPS consists of 32 ATCA Carrier boards, each equipped with four Advanced Mezzanine Cards (AMCs) called LATOME. The LATOME is built around a high-performance and state-of-the-art FPGA, an ARRIA-10 from Intel FPGA (formerly ALTERA).

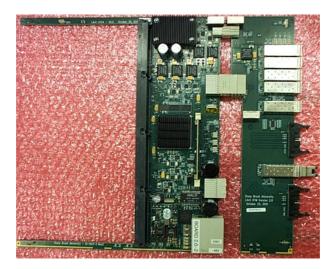

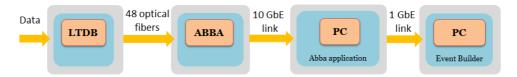

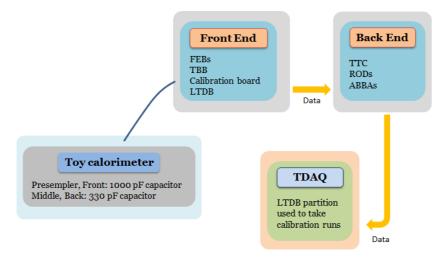

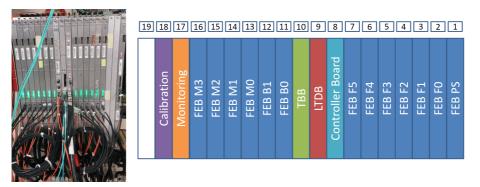

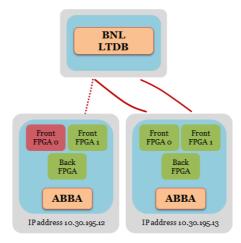

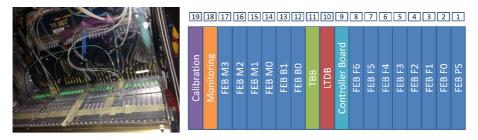

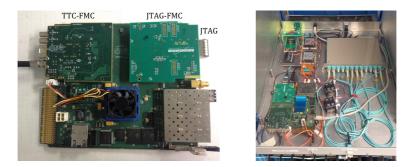

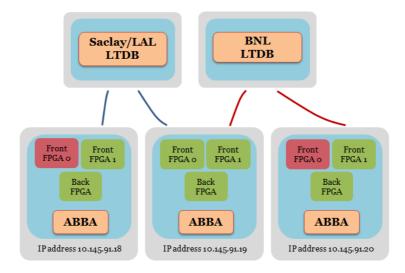

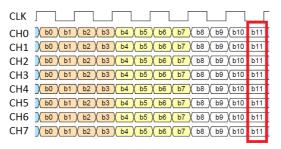

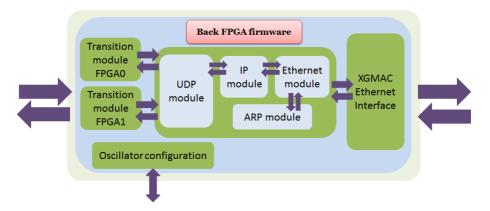

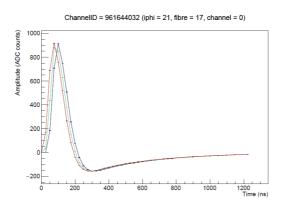

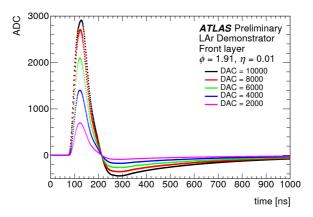

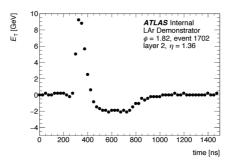

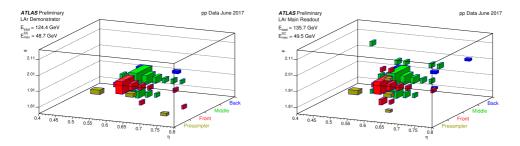

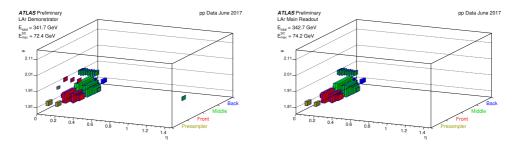

Currently, a demonstrator of the Phase-I upgrade electronics is installed in the ATLAS detector and is collecting physics data from the calorimeter barrel. This is a pre-prototype of the future system covering 1/32 of the barrel region. The goal of the demonstrator is to gain experience on this system with real collision data and validate the LDPS algorithms, including the one for the energy reconstruction of the calorimeter signal. Two LTDB pre-prototypes are installed on a LAr front-end crate. The digitized calorimeter data are transmitted along optical links to three back-end pre-prototype boards called ABBA (ATCA test Board for Baseline Acquisition). ABBA makes use of three Stratix-IV Intel FPGAs for the data readout.

In addition, a test system for the LDPS is installed in the LAr Electronics Maintenance Facility (EMF) laboratory: the system is made of three Carrier boards and two LATOMEs. The purpose is to confirm all the back-end functionalities and ensure the stability of the system before the mass production and the installation in the detector. A new demonstrator system, with both LTDB and LDPS, will be placed in the ATLAS detector in January 2018.

#### LAr Phase-I demonstrator

Chapter 5 gives an overview of the work done in the framework of the demonstrator system for the Phase-I upgrade.

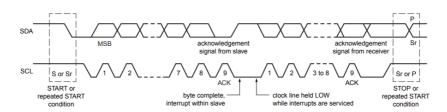

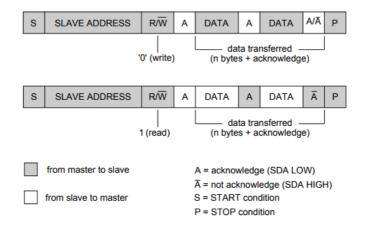

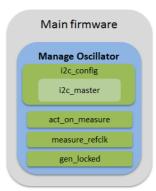

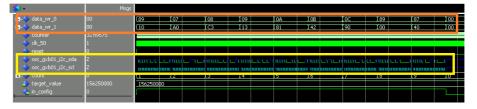

During the first Ph.D. year, I completed my qualification task to become an ATLAS author, implementing an I2C communication protocol to generate specific clock frequencies from crystal oscillators mounted on all ABBA boards. When installed in the detector, ABBA needed two loading steps to work properly. In the first step, the Altera embedded NIOS II processor firmware to set the reference clock frequency via I2C communication with a crystal oscillator, was loaded. Then, the main firmware was loaded in the ABBA board. The aim of this project was to integrate the frequency settings in the main firmware, having only one loading step.

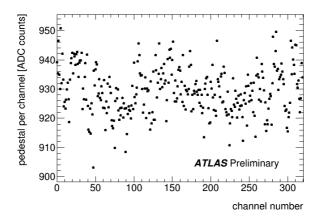

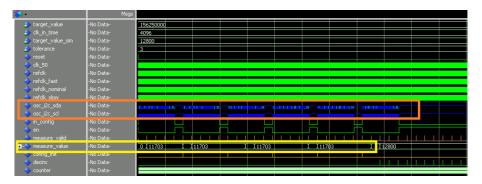

The ABBA firmware was affected by data corruption during the readout of the calorimeter data. During the second year of the Ph.D., I gained a deep knowledge of the firmware, that allowed me to resolve the existing issues and improve the data quality.

<sup>&</sup>lt;sup>1</sup>ATLAS uses a right-handed coordinate system with its origin at the nominal interaction point (IP) in the centre of the detector and the z-axis along the beam pipe. The x-axis points from the IP to the centre of the LHC ring, and the y-axis points upwards. Cylindrical coordinates (r,  $\phi$ ) are used in the transverse plane,  $\phi$  being the azimuthal angle around the z-axis. The pseudorapidity is defined in terms of the polar angle  $\theta$  as  $\eta = -\ln \tan(\theta/2)$ . Angular distance is measured in units of  $\Delta R = \sqrt{(\Delta \eta)^2 + (\Delta \phi)^2}$ .

The reset is a key component of the firmware. It allows to clean errors and bad behaviour, bringing back the system to a clear condition or to the initial state. The ABBA firmware has a complex structure and with the original reset connection it was difficult to reach and recover some firmware blocks. I led the effort to rethink the reset tree, to be able to reach the critical blocks independently and cure on-line instabilities.

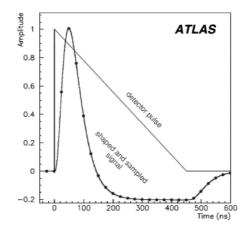

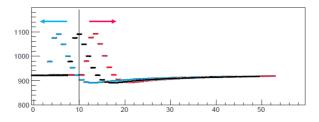

In addition, I implemented a latency auto-correction to ensure the alignment of the calorimeter pulse inside the readout window. The misalignment was happening because of the uncertainty of the phase of the hardware transceivers locking after each reset at the beginning of the data taking. LTDBs make use of a K-comma symbol, an 8 bit pattern that can be used to find and verify the boundaries of a bitstream and for synchronization. This pattern is sent once for each bunch revolution. Knowing that also ABBA is receiving the bunch revolution information, I implemented an auto-alignment such that the pulse on a specific fiber has a constant latency.

#### Firmware development for LATOME

Chapter 6 is about the development and test of the VHDL code for the system-test for the Phase-I upgrade back-end electronics.

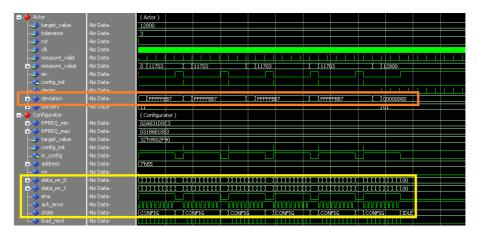

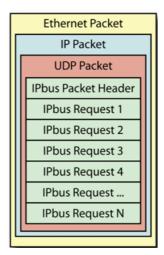

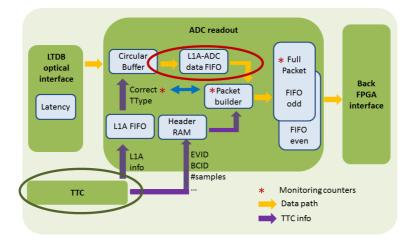

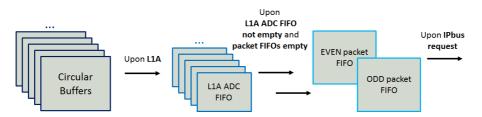

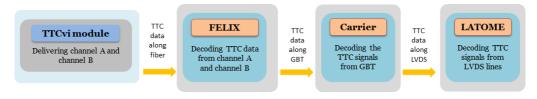

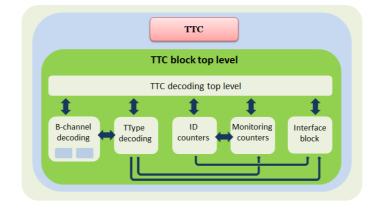

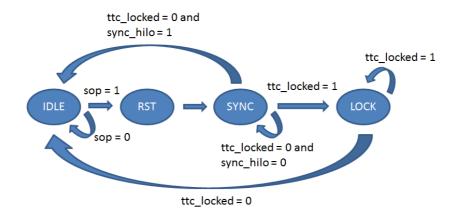

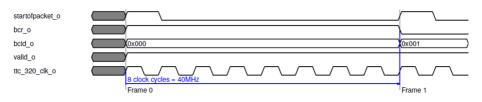

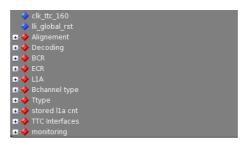

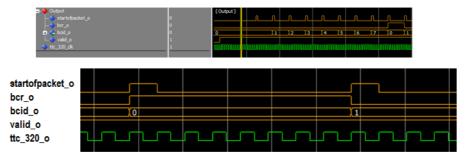

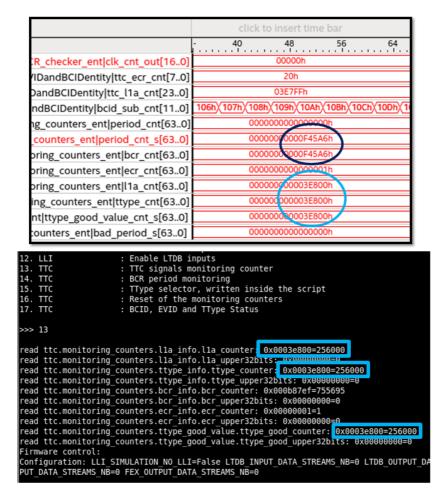

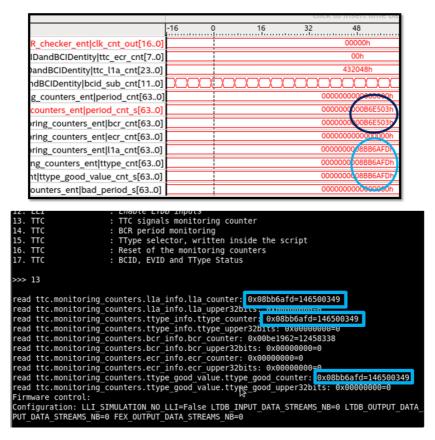

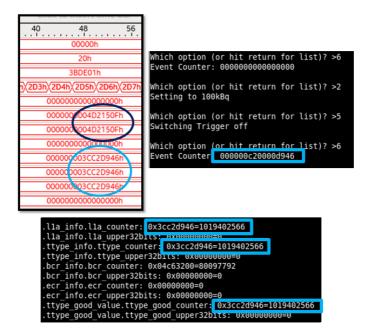

During the last Ph.D year, I worked on the firmware development for the FPGA of the LATOME board. I was asked to be in charge of the firmware module for decoding the TTC signals coming from the LHC central trigger processor. The TTC system allows the timing and trigger signals (such as the LHC clock or the hardware-based first level trigger) to be distributed to the entire experiment. TTC signals are also responsible for the detectors and sub-detectors synchronization. In the LDPS system, the TTC arrives to the Carrier board using the CERN GigaBit Transceiver (GBT) architecture and transmission protocol. On the Carrier the TTC is decoded, re-encoded and sent with a custom protocol along LVDS lines to the LATOME board.

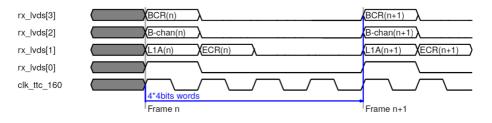

The TTC information is sent along two channels: channel A and channel B. Channel A carries only a one bit information, the hardware-based first level trigger, called Level-1 Accept (L1A). The data stream coming along the channel B can be of two types: broadcast commands or individually-addressed commands/data. Broadcast commands are used to deliver messages to all TTC destinations in the system while individuallyaddressed commands/data are used to transmit user-defined data and commands over the network to specific addresses and sub-addresses.

Along the short broadcast command, two important values are sent: the Bunch Counter Reset (BCR) and the Event Counter Reset (ECR). These two value are used to reset/increase the counters (BCID and EVID) labelling the data accepted by the trigger. Along the long address command, another important information is sent: the Trigger Type (TType). The TType indicates which sub-detector or sub-system fired the trigger.

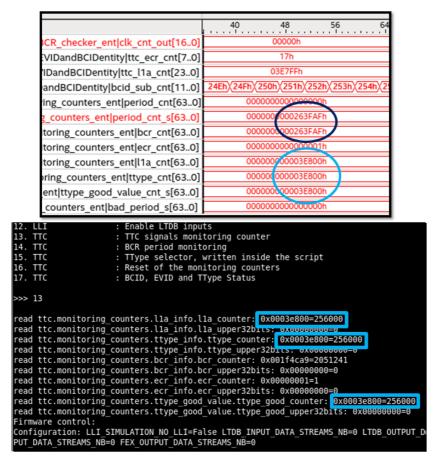

I developed a dedicated module for the TTC with a stable signal decoding and wrote custom interfaces towards other firmware modules. The Input Stage (IStage) firmware module of the LATOME is in charge of aligning the data coming from the LTDB. This is done comparing the BCID computed by my block with the BCID information coming from the LTDB. I implemented all the BCR-related signals on the requested clock domain along a custom interface. At the same time I took care of decoding and providing L1A, ECR and TType signals to the TDAQ and monitoring module, on custom interfaces. This module, together with the ATLAS software, will monitor the data quality and integrity during the data taking.

Furthermore, I am actively taking part in the integration campaigns that are ongoing at EMF for testing the system. A LATOME firmware version comprising the TTC block

was fully tested, monitoring the TTC status through specific TTC registers, to assure that the system complies with the requirements. A prototype of the LDPS system, one ATCA Carrier board and two LATOMEs, running the firmware to which I am contributing, will be installed in ATLAS at the beginning of January 2018.

## Cern and LHC

## 1.1 CERN

CERN, from the French acronym "Conseil Européen pour la Recherche Nucléaire", or European Council for Nuclear Research, was founded in 1952 with the idea of establishing a fundamental physics research organization in Europe. At that time, pure physics research was concentrated on the understanding the atoms and their constituents, explaining why its name contains the word "nuclear".

Nowadays, the understanding of matter goes much deeper than the nucleus and CERN main area of research is particle physics – the study of the fundamental constituents of matter and of the forces acting between them.

At CERN, physicists and engineers are probing the fundamental structure of the universe and they use the world's largest and most complex scientific instruments to study the basic constituents of matter.

#### 1.1.1 The beginning

After the World War II, a first general idea of a re-unified Europe came form Winston Churchill during a speech given at the University of Zurich on the 19th September 1946:

This noble continent, comprising on the whole the fairest and the most cultivated regions of the earth, enjoying a temperate and equable climate, is the home of all the great parent races of the western world.

[...] It is the origin of most of the culture, the arts, philosophy and science both of ancient and modern time. If Europe were once united in the sharing of its common inheritance, there would be no limit to the happiness, to the prosperity and the glory which its three or four hundred million people would enjoy.

It is to re-create the European Family, or as much of it as we can, and to provide it with a structure under which it can dwell in peace, in safety and in freedom. We must build a kind of United States of Europe. [...] If we are to form the United States of Europe, or whatever name it may take, we must begin now.

(EU archives [1])

Also from the scientific point of view, Europe was no longer leading the field.

Following the example of other international organizations, a group of scientists had the idea to create a European atomic physics laboratory. Raoul Dautry, Pierre Auger and Lew Kowarski in France, Edoardo Amaldi in Italy and Niels Bohr in Denmark were among these pioneers. Such a laboratory would not only unite European scientists but would also allow them to share the increasing costs of nuclear physics facilities. The French physicist Louis de Broglie put the first official proposal for the creation of a European laboratory at the European Cultural Conference, in Lausanne on 9 December 1949. A further push came at the fifth UNESCO General Conference, held in Florence in June 1950, where it was emphasized to "assist and encourage the formation of regional research laboratories in order to increase international scientific collaboration...". Finally, during an intergovernmental meeting of UNESCO in Paris in December 1951, the first resolution concerning the establishment of a European Council for Nuclear Research was adopted. Two months later, 11 countries signed an agreement establishing the provisional council. CERN was born.

#### 1.2 The Large Hadron Collider (LHC)

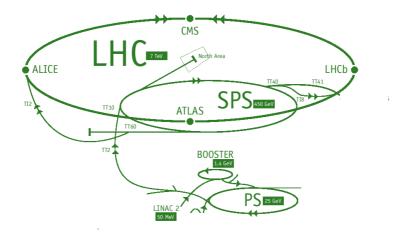

LHC [2] is a two-ring superconducting collider placed at 100 m underground with a circumference of 27.6 km able to accelerate counter-rotating proton beams to a center of mass energy  $\sqrt{s} = 13$  TeV <sup>1</sup> and lead ions (Pb) to 2.8 TeV per nucleon. The two beams collide in four points, as shown in Figure 1.1. Four experiments are placed around these points: ATLAS (A Toroidal LHC ApparatuS) [3], CMS (Compact Muon Solenoid) [4], LHCb (LHC-beauty) [5] and ALICE (A Large Ion Collider Experiment) [6].

Figure 1.1: The CERN accelerator system [7].

The LHC project started in the 1980s, when the scientific community began to design a high energy physics collider able to deliver a center of mass energy higher than the other already existing colliders (LEP and Tevatron). The main purpose of this new machine was the investigation of the nature of electroweak symmetry breaking and the

<sup>&</sup>lt;sup>1</sup>LHC was designed to run at a maximum collision energy of 14 TeV. However some dipole magnets have problems to reach their nominal field and would need to be retrained, demanding a larger number of quenches. It has been decided so far to operate at 13 TeV and to postpone this time-consuming operation to a later date.

search for physics beyond Standard Model at the TeV scale: this included the search for the Higgs boson [8, 9].

The approval for the LHC construction arrived in December 1994 and between 1996 and 1998, the four experiments received official approvals and started the construction. LEP was dismantled in 2000 and the tunnel hosting it is now used by LHC. LEP had eight crossing points while for LHC four interaction points were chosen. Two of them were equipped with new underground caverns.

The center of mass energies reachable at the LHC is much higher respect to ones achieved by the previous experiments. As shown in Figure 1.1, several steps are needed to reach the center of mass energy of  $\sqrt{s} = 13$  TeV:

- in a hydrogen container, electrons are stripped from the atoms to get protons

- inside Linac2 protons energy is raised to 50 MeV

- the circular Booster (PSB) accelerates them to 1.4 GeV

- in the Proton Synchrotron (PS) protons reach 25 GeV

- then in the Super Proton Synchrotron (SPS) particles are accelerated to 450 GeV.

After these steps, protons are finally transferred to the LHC where each beam is accelerated for 20 minutes to 6.5 TeV. The beams are injected in bunches  $\sim 5.1$  cm long and nominally spaced by 25 ns. Bunch crossings occur at a frequency of 40 MHz. Proton beams can circulate for many hours inside the LHC under normal operating conditions [7, 10].

#### 1.2.1 ATLAS and CMS

ATLAS and CMS are two general-purpose detectors used to investigate the largest range of physics possible. They were built to take advantage of the full discovery potential of the accelerator. Several physics areas are under study: the search for supersymmetric and exotic particles, the accurate measurement of the top and Higgs properties and Standard Model [11] precision measurements.

Although the scientific goals are the same, different technical solutions are used. The independent design is very important in order to have the possibility to reduce systematic errors and cross-confirm any new discovery. An example of different detector solutions is the magnet system. ATLAS is characterized by a solenoid magnet producing a 2 T magnet field along the beam and a toroidal magnet system. The outer toroidal magnetic field is produced by eight very large air-core superconducting barrel loops and two end-caps air toroidal magnets, all situated outside the calorimeters and within the muon system. The CMS detector is built around a solenoid magnet, a cylindrical coil of superconducting cable that generates a field of 4 T. The field is confined by a steel yoke that forms the bulk of the detector 14000-tonne weight.

#### 1.2.2 ALICE and LHCb

ALICE and LHCb are detectors optimized for the study of specific phenomena.

ALICE studies heavy ions collisions to understand the behaviour of high energy nuclei interaction. It is designed to investigate the physics of strongly interacting matter at extreme energy densities, where quark-gluon plasma forms. For this reason each year LHC provides some weeks with lead-ions collisions. ALICE collects also proton-proton collision data to calibrate and to support the other detectors measurements. LHCb experiment is specialized in B hadron study and aims to investigate their properties which would help in understanding the difference in the quantity of matter and anti-matter in the universe. Like ALICE, the LHCb experiment is asymmetric and mainly focused on the forward region.

### 1.3 LHC 2017 achievements and future perspectives

After the Higgs boson discovery in 2012 [8, 9], the LHC experiments continued to study the Higgs boson properties to confirm the Standard Model predictions and search for new physics phenomena.

During the 2017, the LHC experiments published several new results [12]. Both ATLAS and CMS used data from 2015 and 2016 to establish evidence for Higgs boson decays to two bottom quarks [13] and CMS also presented a "5-sigma" observation of Higgs boson decays to two tau particles [14]. Furthermore, both ATLAS and CMS saw evidence of "ttH production", one of the rarest processes measured at the LHC [15, 16]. The two experiments combined their top quark measurements from proton-proton collisions, on the production of a top quark and a Z boson, a rare electroweak process [17]. In addition, CMS observed top quarks from proton-lead collisions [18] and ATLAS presented high-precision measurements of the top quark mass [19] and of the W-boson mass [20]. CMS also measured the forward-backward asymmetry in Z boson decays to electrons and muons [21, 22].

In order to continue exploiting the physics frontier, upgrades of the LHC and higher luminosity are planned for the next years [23].

Further studies and measurements of the properties of the Higgs boson will be done through the possible Higgs boson production processes and decay final states (some studies are already available here [24]).

The enhancement of the performance of the calorimeter and tracker systems in the forward region foreseen for the Phase-II upgrade will be crucial to study Higgs bosons produced via Vector-Boson Fusion (VBF). To distinguish this production mode, forward jets (in the region  $|\eta| \ge 2.5$ ) are reconstructed.

Study on the Vector-Boson Scattering (VBS) are foreseen as well. This process is characterised by high- $p_T$  jets and it will be crucial to determinate if other mechanisms, together with the 125 GeV Higgs boson, are responsible for maintaining unitarity.

Finally, the studies on SUperSYmmetry (SUSY) and Beyond Standard Model (BSM) Physics will continue.

## 1.4 LHC plan

In Figure 1.2 a detailed schedule of LHC is shown:

- Long Shutdown 1 (LS1): 2013-2014. This shut-down was used to consolidate machine elements (repairing the magnet splices and upgrading the collimation scheme) in order to achieve the design beam energy and luminosity.

- Run 2: 2015-2018. The LHC is colliding beams at  $\sqrt{s} = 13$  TeV since 2015, and has exceeded the design peak luminosity of  $L = 10^{34} cm^{-2} s^{-1}$  (about  $2 \times 10^{34} cm^{-2} s^{-1}$  as of October 2017). An integrated luminosity of 75-100 fb<sup>-1</sup> is expected to be delivered to ATLAS and CMS during the 3 years of running in Run 2.

- Long Shutdown 2 (LS2): 2019-2020. The Linac4 will be connected into the injector complex, and the injection beam energy of the Proton Synchrotron Booster will be

| LHC                          |                                                           |                    |                      |                                                      |                                               |                               | HL-LHC                            |         |

|------------------------------|-----------------------------------------------------------|--------------------|----------------------|------------------------------------------------------|-----------------------------------------------|-------------------------------|-----------------------------------|---------|

| Run 1                        |                                                           | Run 2              |                      |                                                      | Run 3                                         |                               | Run 4 - 5                         |         |

|                              | LS1                                                       | 13-14 TeV EYETS    |                      | LS2                                                  | 14 TeV                                        | LS3                           | 14 TeV                            | - energ |

| 7 TeV 8 TeV                  | splice consolidation<br>button collimators<br>R2E project |                    |                      | injector upgrade<br>cryo Point 4<br>Civil Eng. P1-P5 | cryolimit<br>interaction<br>regions           | HL-LHC installation           | 5 to 7 x<br>nominal<br>luminosity |         |

| 2011 2012                    | 2013 2014                                                 | 2015 2016 201      | 7 2018               | 2019 2020                                            | 2021 2022 2023                                | 2024 2025                     | 2026 <b>2037</b>                  |         |

| 75%<br>nominal<br>luminosity | experiment<br>beam pipes                                  | nominal luminosity | (                    | experiment upgrade<br>phase 1                        | radiation<br>damage<br>2 x nominal luminosity | experiment upgrade<br>phase 2 |                                   |         |

| 30 fb <sup>-1</sup>          |                                                           |                    | 150 fb <sup>-1</sup> |                                                      | 300 fb <sup>-1</sup>                          |                               | 3000 fb <sup>-1</sup>             | tegrate |

Figure 1.2: LHC plan [25].

upgraded in order to reduce the beam emittance. New cryogenics plants will be installed to separate the cooling of the superconducting radio frequency modules and the magnet cooling circuit.

- Run 3: 2021-2023. The LHC design parameters should allow for an ultimate peak instantaneous luminosity of  $L \sim 2.2 \times 10^{34} cm^{-2} s^{-1}$  (Phase-I operation) and for delivering an integrated luminosity of  $\sim 300$  fb<sup>-1</sup> during Run 3.

- Long Shutdown 3 (LS3): 2024-2026. The LHC will undergo a major upgrade of its components, like low-β quadrupole triplets and the use of crab cavities at the interaction regions.

- High-Luminosity LHC (HL-LHC): 2026-2030 and beyond. The LHC complex will deliver levelled instantaneous luminosity up to  $L = 7.5 \times 10^{34} cm^{-2} s^{-1}$  (Phase-II operation) with the goal of providing an ultimate integrated luminosity of up to 4000 fb<sup>-1</sup> (since Figure 1.2 was produced, the value has been updated) after a period of about 12 years.

## 1.5 ATLAS upgrade plan

In the next years, ATLAS will have to cope with luminosities beyond the LHC nominal design value, maintaining the same physics performance.

The detector upgrade foreseen for the Phase-I operation will allow ATLAS to maintain low transverse momentum ( $p_T$ ) trigger thresholds by increasing the granularity of the calorimeters involved in the Level-1 trigger and by introducing new muon trigger in the forward direction. Fast accurate tracking information provided near the start of the Level-2 trigger processing will lead to much more effective identification of the events. The full functionality of all the detector elements has to be preserved to keep the excellent capabilities of ATLAS. Simulations and detector performance extrapolations suggest that changes and upgrade of the sub-detectors should not be required until Phase-II [26].

From 2026, the ATLAS detector will have to meet the challenges and take advantage of operating at the HL-LHC. This will present a unique opportunity to extend the mass reach in searches for many signatures of new physics and to significantly extend the study of the properties of the Higgs boson. The current Inner Tracker will be no longer suitable for long term operations. It will be replaced with new silicon trackers to maintain the performance. The very high luminosities also present significant challenges to the operation of the rest of the detector systems as well as of the trigger. A new trigger architecture will be implemented exploiting the upgrades of the detector readout systems that will improve the event selection [27].

## ATLAS

## 2.1 Structure of the ATLAS detector

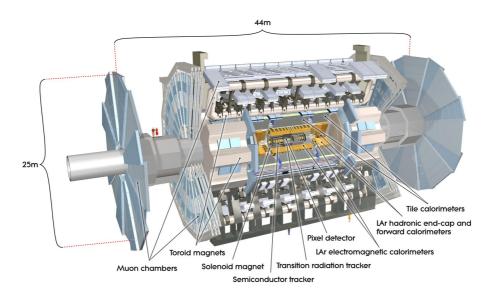

ATLAS is one of the two general-purpose detectors at the Large Hadron Collider (LHC). It has a cylindrical shape, with a diameter of 25 m and a length of 46 m. It weighs approximately 7000 tons. Figure 2.1 shows the structure of the detector:

Figure 2.1: A schematic view of the ATLAS detector [28].

ATLAS is organised in layers of detectors and consists of three major components: the inner tracker, the calorimeters and the muon system. A solenoidal magnet is placed between the inner tracker and the calorimeters, while three toroidal magnet systems are used to identify and measure the momentum of muons. ATLAS has been built to cover as much as possible of the solid angle around the interaction point.

#### 2.1.1 Coordinate system

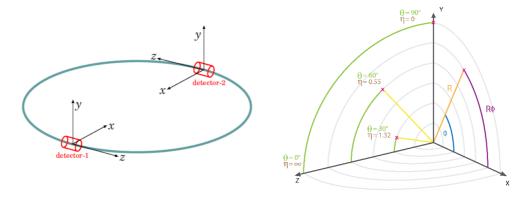

A common coordinate system is used in the ATLAS experiment. The interaction point is defined as the origin of the coordinate system, the beam direction defines the z-axis and the x-y plane is transverse to the beam direction. The positive x-axis points from

the origin of the coordinates to the center of the LHC ring and the positive y-axis points upward to the surface of the earth, as shown on the left side of Figure 2.2. Important physics quantities like the transverse momentum  $p_T$ , the transverse energy  $E_T$  and the missing transverse energy  $E_T^{miss}$  are all defined in the x-y plane. The positive z-values

Figure 2.2: Common coordinate system used in the LHC experiments.

are usually referred to the half of the detector called "A-side" while the negative values refer to the other half, called "C-side". Furthermore, the transverse plane can be also described with  $r - \phi$  coordinates.

As shown on the right side of Figure 2.2, the azimuthal angle  $\phi$  is measured from the positive x-axis. The polar angle  $\theta$  is defined as the angle from the positive z-axis, along the detector. The radial coordinate r, describes the distance from the beam.

Usually the pseudorapidity  $\eta$  is used instead of the polar angle  $\theta$ :

$$\eta = -\log \tan \frac{\theta}{2},\tag{2.1}$$

and the angular distance  $\Delta R$  between two objects in the  $\eta - \phi$  space:

$$\Delta R = \sqrt{\Delta \eta^2 + \Delta \phi^2}.$$

(2.2)

The difference in pseudorapidity  $\eta$ , as well as  $\Delta R$ , are important as they are Lorentz invariant under boosts along the z-axis.

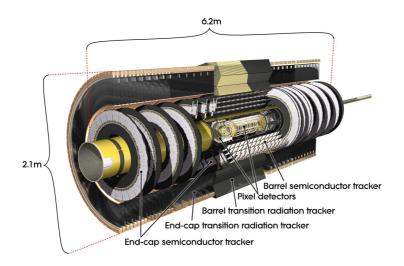

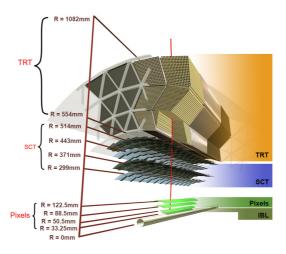

#### 2.2 Inner Detector

The Inner Detector (ID) [29] covers a pseudorapidity range of  $|\eta| < 2.5$  and performs particle tracking in order to measure particle transverse momentum and trajectories. The ID diameter is 2.1 m and the total length is 6.2 m. A schematic picture of the ID is shown in Figures 2.3 and 2.4. The ID is made of three subsystems: Pixel detector [30], Semi-Conductor Tracker [31] and Transition Radiation Tracker [32]. During 2014, a new pixel detector layer was inserted, the Insertable Barrel Layer detector [33]. In the barrel region the high-precision detectors are arranged in concentric cylinders around the beam axis, while the end-cap detectors are mounted on disks perpendicular to the beam axis. The high-resolution detectors at the inner radii and the tracking elements at the outer radii are both inside a solenoidal magnet with a central magnetic field of 2 T.

Figure 2.3: A schematic view of the Inner Detector [34].

#### 2.2.1 Pixel detector

The pixel detector system is the innermost element of the ID. It is designed to provide a very high-granularity, high-precision set of measurements as close to the interaction point as possible. Silicon pixels, with their excellent spatial resolution, play a very important role in the identification and reconstruction of primary and secondary vertices, respectively from the proton-proton interaction and from the decay of particles, for example containing a b-quark or for b-tagging of jets.

The system consists of three barrels at average radii of ~50.5, 88.5 and 122.5 mm, and four disks on each side, between radii of 110 and 200 mm, which complete the angular coverage. All pixel modules are identical, the silicon wafer size is  $16.4 \times 60.8$  mm and  $250 \mu$ m thick. Each sensor has about 46 thousand pixels sensors of size  $50 \times 400 \mu$ m. There are 1744 modules in the Pixel Detector for nearly 80 million channels. The resolution is of 14  $\mu$ m in  $R - \phi$  and 115  $\mu$ m in z(R) in the barrel (end-cap).

#### 2.2.2 Insertable B-Layer

The performance of the innermost layer of the Pixel detector is fundamental for vertexing and b tagging. This layer was exposed to a very high radiation dose and this had an impact on its performances, even if it was designed with radiation hardness techniques. For this reason, an additional pixel layer inside the B-layer, the Insertable B-Layer (IBL), has been inserted during the LHC shut down in 2013.

In the IBL, two different silicon sensor technologies have been used: planar n-in-n and 3D with passing through columns. The planar pixel technology is used in the barrel region while the 3D technology is used in the forward region. The two types of sensors have respectively a thickness of 200 and 230  $\mu$ m and a pixel size of  $50 \times 250 \ \mu\text{m}^2$ .

The inner radius of the IBL detector is 31 mm while the outer radius is 40 mm. The insertion gap between the inner supporting tube and the IBL detector is only 0.2 mm and the gap between the supporting tube and the Pixel is 1.9 mm. To make the integration possible the diameter of the beam pipe was reduced.

Figure 2.4: A schematic view of the Inner Detector, including the new IBL [34].

#### 2.2.3 Semi-Conductor Tracker

The Semi-Conductor Tracker detector (SCT) is positioned outside of the Pixel detector. It comprises four central barrel layers at radii of 299, 371, 443 and 514 mm and two end-caps which contain nine disks each.

Each silicon sensor is  $63.56 \times 63.96 \text{ mm}^2$  with 768 readout strips each with 80  $\mu$ m pitch. The barrel part is made of 2112 modules while the end-cap carries 1976 modules. Each barrel module includes four silicon microstrip sensors and the readout electronics: two pairs of sensors are mounted back-to-back with a 40 mrad stereo angle to make a double sided module. The forward modules are very similar in construction but use tapered strips. The detector contains 61 m<sup>2</sup> of silicon detectors, with 6.2 million readout channels. The space-point resolution per module is 17  $\mu$ m in  $R - \phi$  and 580  $\mu$ m in z(R) in the barrel (end-cap).

#### 2.2.4 Transition Radiation Tracker

The Transition Radiation Tracker (TRT) is the outermost of the three tracking subsystems of the ID. The TRT is a gaseous straw-tube tracker and consists of drift tubes with a diameter of 4 mm. In the centre of each tube there is a gold-plated tungsten wire of 31  $\mu$ m diameter. When a charged particle traverses the TRT, it ionises the gas inside the straws and the resulting free electrons drift towards the wire, where they are collected. The TRT detector combines tracking capabilities with particle identification based on transition radiation photon detection. The particle identification functionality gives significant discrimination power between electrons and charged pions with energy in the range 1 GeV < E < 100 GeV.

The tube wall is kept at a voltage of -1.5 kV and the wire at ground potential, so that each tube acts as a small proportional counter and is filled with a non-flammable xenon-based gas mixture of 70% Xe, 20% CO<sub>2</sub> and 10% CF<sub>4</sub>. During Run 1, due to some leaks which developed in the gas system, in some regions the Xenon gas was replaced by a much cheaper Argon-based gas mixture.

The barrel section is built of individual modules between 329 and 793 straws each, covering the radial range from 554 to 1082 mm. Each end-cap consists of 18 wheels

covering a radial range from 640 to 1030 mm, and 830 to 3400 mm along the z-axis.

The total number of TRT readout channels is approximately 420000. The TRT only provides  $R - \phi$  information in the barrel and  $z - \phi$  in the end-cap, with a resolution of about 130  $\mu$ m per straw.

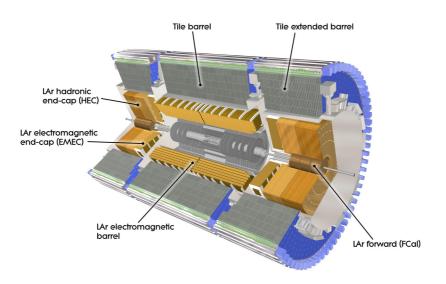

#### 2.3 Calorimeters

As shown in Figure 2.5, the components of the ATLAS calorimetry system are: the Liquid Argon (LAr) calorimeter [35] and the Tile hadronic calorimeter [36].

Figure 2.5: A schematic view of the ATLAS calorimeters [37].

#### 2.3.1 LAr calorimeter

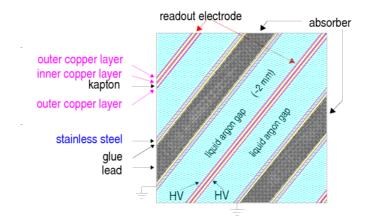

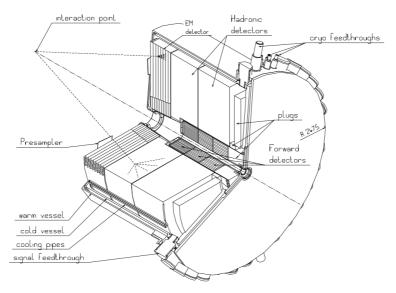

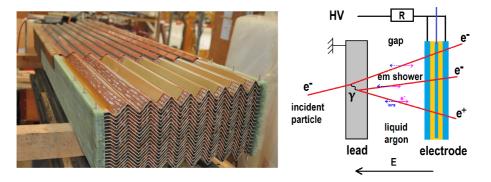

The LAr electromagnetic calorimeter uses a sampling liquid argon/lead technology in the barrel and end-cap electromagnetic calorimeter and liquid argon/copper in the hadronic end-caps. It is hosted by three large aluminium cryostats. The LAr calorimeter can be divided in four major parts: the Electro-Magnetic Barrel (EMB), the Electro-Magnetic End-Cap (EMEC), the Hadronic End-Cap (HEC) and the Forward Calorimeter (FCal).

The EMB is 6.4 m long, 53 cm thick and covers the pseudorapidity range  $|\eta| < 1.475$  providing signals from about 110000 channels. The EMB consists of two barrels of 1024 lead absorbers, interleaved with the same number of electrodes held in place by a 2.1 mm high honeycomb structure, which defines the liquid argon gap size. The radiation length (X<sub>0</sub>), which will be described in section 3.2, in this  $\eta$ -region is about 24X<sub>0</sub>.

The EMEC extends the pseudo rapidity coverage to the range  $1.375 < |\eta| < 3.2$ , and, as the EM barrel, is built with accordion shaped absorbers and electrodes, providing an excellent hermeticity, a complete azimuthal coverage and longitudinal segmentation. There are 256 absorbers for the inner wheel ( $1.375 < |\eta| < 2.5$ ), and 768 for the outer

wheel (2.5 <  $|\eta|$  < 3.2). The EMEC is 0.632 m thick and has a radius of 2.077 m. In this  $\eta$ -region the radiation length value is about 30X<sub>0</sub>.

The HEC calorimeters consist of two cylindrical wheels in each end-cap. Each wheel is made of 32 wedge-shaped modules. Each of them is an alternation of 25 mm thick copper absorbers (50 mm in the second wheel), and signal collection gaps. The HEC wheels have a radius of 2.09 m.

The FCAL calorimeter uses cylindrical electrodes consisting of rods positioned in the center of tubes parallel to the beam axis with liquid argon filling the small gaps between the rod and the tube wall. The tubes are substained by a metal matrix. The FCAL consists of three modules: the one closest to the interaction point uses copper as absorber and is optimized for electromagnetic measurements. The other two modules use tungsten and are optimized for hadronic measurements [38].

#### 2.3.2 Tile calorimeter

The Tile hadronic calorimeter is a large sampling calorimeter which makes use of iron as the absorber material and scintillating tiles as the active medium. The Tile calorimeter consists of a cylindrical structure with an inner radius of 228 cm and an outer radius of 423 cm. It is subdivided into a 564 cm long central barrel and two 291 cm extended barrels, each composed of 64 modules along  $\phi$ . The barrel covers the region  $-1.0 < |\eta| < 1.0$ , and the extended barrels cover the region  $0.8 < |\eta| < 1.7$ . The Tile calorimeter has an effective nuclear interaction length of  $\lambda = 20.7$  cm, with a total depth of  $7.4 \lambda$  at  $\eta = 0$ . Furthermore, the magnetised steel of the hadronic calorimeter and its girder structure serve to return the flux of the solenoid magnetic field.

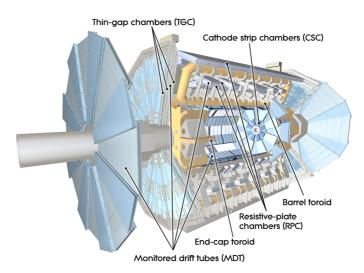

#### 2.4 Muon system

The ATLAS outermost sub-detector is the muon spectrometer [39]. It provides muon momentum measurements using the muon track deflection by three large superconducting toroid magnets. A schematic view of the muon system is shown in Figures 2.6.

Figure 2.6: A schematic view of the ATLAS muon system [40].

In the barrel region, tracks are measured in chambers arranged in three cylindrical layers (stations) around the beam axis. In the transition and end-cap regions, the chambers are installed vertically, in three stations as well. A precision measurement of the track coordinates in the principal bending direction of the magnetic field is provided by Monitored Drift Tubes (MDTs) over most of the pseudorapidity range. At large pseudo-rapidities and close to the interaction point, Cathode Strip Chambers (CSCs) with higher granularity are used to sustain the very high rate and the background conditions. In order to meet the very stringent momentum resolution requirements, an optical alignment system has been designed [41].

The trigger system covers the pseudorapidity range  $|\eta| < 2.4$ . Resistive Plate Chambers (RPCs) and Thin Gap Chambers (TGCs) are used respectively in the barrel and in the end-cap regions. Both types of trigger chambers also provide a second-coordinate measurement of tracks orthogonal to the precision measurement, in a direction approximately parallel to the magnetic field lines.

In the pseudorapidity range  $|\eta| < 1.0$ , the bending is provided by a large barrel magnet made of eight coils surrounding the hadron calorimeter. For  $1.4 < |\eta| < 2.7$ , muon tracks are bent in two smaller end-cap magnet systems inserted into both ends of the barrel toroid. In the interval  $1.0 < |\eta| < 1.4$  the deflection is provided by a combination of barrel and end-cap fields. This configuration provides a magnet field that is mostly orthogonal to the muon trajectories and minimizes the degradation of resolution due to multiple scattering.

The muon system design provides a good momentum measurement of muons even at high energy: the transverse momentum  $p_T$  can be measured with a resolution of  $\Delta p_T/p_T = 10\%$  even at  $p_T = 1$  TeV.

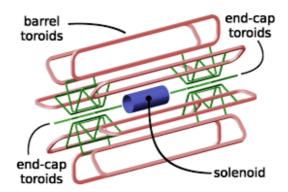

#### 2.5 Magnet system

The main sections of the magnet system are the central solenoid magnet [42], the barrel toroid [43] and the end-cap toroids [44], as shown in Figure 2.7.

**Figure 2.7:** A schematic view of the ATLAS magnet system. The toroidal magnet is made of the red and the green part. The solenoid is shown in blue [45].

The solenoidal magnet is placed between the inner detector and the calorimeter system. It's 5.3 m long, with a diameter of 2.4 m and a weight of 5 ton. The solenoid produces a 2 T magnetic field in the central tracking volume. The operating temperature of 4.5 K is maintained by a cryostat shared with the barrel electromagnetic calorimeter.

The barrel toroid consists of 8 flat superconducting race-track coils, each 25.3 m long and 5 m wide. The 8 coils in the torus are kept in position by 16 support rings. In total the barrel toroid is 830 tons. The magnets are cooled down to 4.5 K by liquid helium and operate at a nominal current of 20.5 kA.

Two end-cap toroids, positioned inside the barrel toroid, at both ends, provide the required magnetic field across a radial span of 1.5 to 5 m. Each end-cap toroid has a weight of 240 tons. The coil system of the end-cap toroid is rotated by an angle of 22.5 with respect to the barrel toroid coil. In this way, radial overlap between the two coil systems is provided and the bending power optimized.

### 2.6 Forward detectors

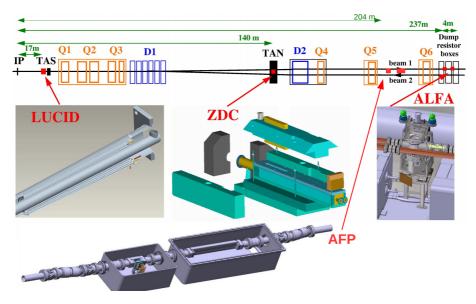

The ATLAS forward region is covered by a group a small sub-detectors. Figure 2.8 shows their position along the beam line, from the closest (left) to the most distant (right) from the collision point: LUCID (Luminosity measurement using Cherenkov Integrating Detector) [46], ZDC (Zero-Degree Calorimeter) [47], AFP (ATLAS Forward Proton) [48] and ALFA (Absolute Luminosity For ATLAS) [49].

Figure 2.8: The ATLAS forward detectors and their distance from the collision point [50].

LUCID is a Cherenkov counter, monitoring the luminosity delivered by the LHC accelerator, in ATLAS. Two detectors are symmetrically placed in both forward regions at 17 m from the interaction point. Each LUCID detector is made of 16 photomultiplier tubes and 4 quartz fiber bundles. The photomultipliers detect charged particles passing through the quartz windows, where Cherenkov light is produced. Cherenkov light is produced in the fiber bundles as well and carried to the photomultipliers.

ZDC has the role of detecting forward neutrons, for  $|\eta| > 8.3$ , in both *pp* and heavyion collisions. It is placed on both sides of the ATLAS detector, at a distance of 140 m. Each detector has one electromagnetic module (about 29 radiation lengths thick), and 3 hadronic modules, composed of tungsten with an embedded matrix of quartz rods, attached to photomultiplier tubes. AFP aims to measure transfer momentum and energy loss of protons emitted from the collision point interaction in very forward directions. Two detectors are located per each ATLAS sides, at 204 m and 217 m, along the beam line. Each detector contains a 3D silicon tracker and a time-of-flight detector in the far stations.

ALFA is the furthest detector, placed at 237 m from the interaction point, on both ATLAS sides. It aims to measure the elastic *pp* scattering at small angles. The set-up is installed in Roman Pot stations [51], vessels that are connected to the accelerator vacuum via bellows. In this way the detector can approach the beam very close without entering the machine vacuum. Each detector is made of staggered layers of square-shaped scintillating fibers, read out by photomultiplier tubes.

## 2.7 Trigger and data acquisition

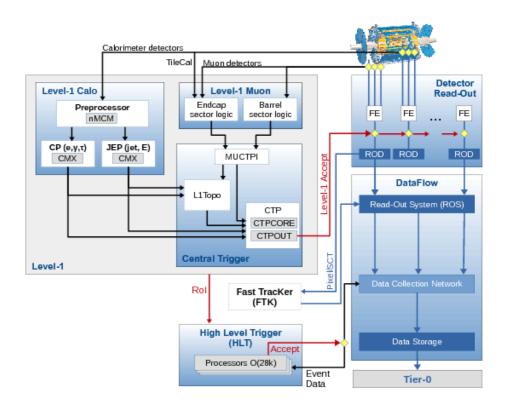

The Trigger and data acquisition (TDAQ) system [52], shown in Figure 2.9, is a fundamental component of the ATLAS detector. Data from collisions is moved from the detector readout electronics into front-end buffers at the bunch crossing rate. The task of the Trigger and DAQ system is to select a few hundred events per second for recording to a permanent storage for later study. The DAQ system has to transport and assembly the event data from the front-end buffers to the recording on disk.

Figure 2.9: The ATLAS trigger and data acquisition system in Run 2 [53].

The bunch crossing rate at the LHC was 20 MHz during Run 1 and was increased to 40 MHz for Run 2. The trigger system has to face high event rates and pile-up levels,

maintaining high efficiency for selecting rare events. A two-level trigger system is used in ATLAS, with each level accepting only a subset of data to be passed on to the next.

The first level trigger (L1) is hardware based and processes data from the calorimeter and the muon detectors. The successive trigger level, called High-Level Trigger, is operated in software and works on a large farm of commercial computer processors.

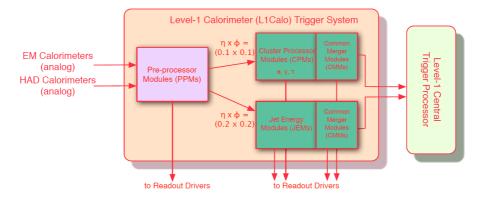

The L1 trigger decision is taken by the Central Trigger Processor (CTP), which receives inputs from the L1 calorimeter (L1Calo) and L1 muon (L1Muon) triggers as well as several other subsystems like the Minimum Bias Trigger Scintillators (MBTS) [54], LUCID Cherenkov counter and the ZDC. After the L1 trigger acceptance, the events are buffered in the Read-Out System (ROS) and processed by the HLT. The HLT receives Region-of-Interest (RoI) information from L1, which can be used for regional reconstruction by the trigger algorithms. After the events are accepted by the HLT, they are transferred to local storage at the experimental site and exported to the Tier-0 facility at CERN's computing centre for offline reconstruction.

## Liquid Argon Calorimeter

## 3.1 Introduction

In particle physics, calorimeters are detectors used to measure the energy of impinging particles. The typical usage of calorimeters is for energy measurements but they can be used as well for providing position and timing information in case of a proper segmentation or particle identification. In this dissertation I give a synopsis of the characteristic of these detectors, while a complete description can be found in [55] and in [56].

The main features of calorimeters can be summarized in the following points:

- The intrinsic energy resolution for a calorimeter increases as  $1/\sqrt{E}$ , where E is the particle energy, in contrast with magnetic spectrometers in which the momentum resolution deteriorates with particle momentum.

- Calorimeters are sensitive to both charged and neutral particles, again in contrast to the behaviour of a magnetic spectrometer. These detectors, if hermetic, can provide an indirect transverse measurement of undetected particles like neutrinos through the so-called "missing energy", through energy balance.

- Calorimeters are versatile detectors. They could be segmented and, in addition to energy, they could provide position information, timing and particle identification information.

- Calorimeters can be used for triggering, as they provide fast signals.

- The shower length increases only logarithmically with the energy of the incident particle. As a consequence, the size of a calorimeter, which aims to contain an entire shower, scales logarithmically with the incident particle energy. On the other side, the dimension of an electromagnetic spectrometer scales with  $\sqrt{p}$  (where *p* is the particle momentum) for a given momentum resolution.

Calorimeters can be divided in electromagnetic calorimeters and hadronic calorimeters. Electromagnetic calorimeters measure mainly electrons, positrons and photons through their electromagnetic interactions with the calorimeter material. Hadronic calorimeters are used to measure mainly hadrons through their strong and electromagnetic interactions. In both cases, the interaction of the impinging particle in the calorimeter produces a cascade of secondary particles, called shower, with degraded energy. The energy deposited by the shower in the calorimeter active medium can be detected and is used to estimate the energy of the incident particle. A calorimeter is linear when there is a constant proportion between the energy deposited and the response: electromagnetic calorimeters are in general linear while hadronic calorimeters are not, unless they are compensated (more details in section 3.3.2).

Calorimeters can be also divided into two other categories, depending on their construction: homogeneous and sampling calorimeters. The material of an homogeneous calorimeter is not only used to degrade the incident particle energy but is also entirely sensitive to the energy deposited by the shower. In a sampling calorimeter, two different materials are used for energy degradation and signal generation. Usually the absorption material is a passive and high-Z medium while the signal is detected in an active low-Z medium.

The rest of this chapter will be mostly dedicated to electromagnetic calorimeters.

#### 3.2 Electromagnetic calorimeter

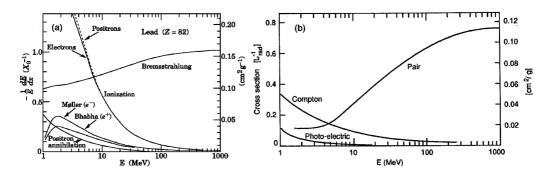

Electrons and photons over 1 GeV mainly interact through bremsstrahlung mechanism (incident electron) and pair production (incident photon) [55]. These processes creates secondary processes where electrons (or positrons) and photons create a cascade of particles with decreasing energy. At a certain point, the particle energy falls below the threshold for pair production and the remaining energy is dissipated by excitation and ionization.

The energy at which radiation loss and collision loss are equally likely is called "critical energy" ( $\epsilon$ ) and is given by [55]:

$$\epsilon(MeV) \approx \frac{800}{Z+1.2}.\tag{3.1}$$

#### 3.2.1 Electromagnetic cascade

An incident electron loses its energy through bremsstrahlung mechanism at an average rate of  $dE/dx = -E/X_0$  where  $X_0$  is called radiation length. This is the mean distance over which a high energy electron loses all but 1/e of its energy and is defined by this equation [55]:

$$X_0 = \frac{(716.4 \, g \, cm^{-2})A}{Z(Z+1)ln(287/\sqrt{Z})},\tag{3.2}$$

where Z and A are the atomic number and atomic weight of the material.

A similar concept exists also for incident photons, the mean free path  $X_{\gamma}$  that is the average distance which a high energy photon can travel before converting into  $e^+e^-$  pair. This is the mean distance over which a group of identical photons lose all but 1/e of their number by pair production and can be defined as:

$$X_{\gamma} = \frac{9}{7} X_0.$$

(3.3)

In general, the longitudinal distribution of an electromagnetic shower scales with the radiation length and the shower depth at which the largest number of secondary particles occur is located at

$$t_{max}(X_0) = \left[ ln \frac{E_{inc}}{\epsilon} + C_i \right], \qquad (3.4)$$

where  $C_e = -0.5$  and  $C_{\gamma} = +0.5$ .

The transverse size of the electromagnetic shower is mainly due to scattered electrons and positrons. Bremsstrahlung photons can also partially contribute to the shower spread. The spread of the electromagnetic shower is given by the Moliere radius [55]:

$$\rho = X_0 \frac{21MeV}{\epsilon}.\tag{3.5}$$

It represents the average lateral deflection of electrons at the critical energy after one radiation length.

A short description of the most important processes, shown in Figure 3.1, is given in the following paragraphs.

**Figure 3.1:** (a) Fractional energy lost in lead by electrons and positrons as a function of energy. (b) Photon interaction cross section in lead as a function of its energy [56].

#### Bremsstrahlung

An electron or a positron with initial energy  $E_{init}$  loses part of its energy trough the deceleration caused by the deflection due to the Coulomb field of an atomic nucleus. The moving particle loses kinetic energy, which is converted into a photon, which usually carries only a fraction of the initial energy of the particle. This radiation is called bremsstrahlung, that in german means "braking radiation" [57].

#### Pair production

If the energy of a photon is at least twice the rest mass of an electron (512 keV), it can produce an electron-positron pair. The cross-section for pair production increases with increasing energy of the incident particle and reaches a plateau for energies above 10 GeV. This process requires the nearby presence of a massive atom for momentum conservation, but the atom recoil energy is negligible [57].

#### **Photoelectric effect**

In the photoelectric absorption process, a photon is absorbed by an atom, leaving it in an excited state. The atom returns to the ground state by emitting an electron, in this case called photoelectron. Photoelectric absorption is more significant for low-energy photons ( $\approx 100 \text{ keV}$ ), increases with the atomic number of the absorber and decreases with the photon energy. The total energy of the process is always conserved [57].

#### **Compton effect**

In the Compton scattering, a photon hits an atomic electron in the absorbing material. The result is a less energetic photon together with a scattered electron, carrying the energy lost by the photon. At the end, the overall momentum of the system is again conserved. The probability of compton scattering is higher at MeV energy range. If the scattered photon still has enough energy, the process may be repeated [57].

#### 3.2.2 Energy resolution

The energy resolution for a calorimeter can be written as [56]:

$$\frac{\sigma(E)}{E} = \frac{a}{\sqrt{E}} \oplus \frac{b}{E} \oplus c \tag{3.6}$$

where  $\oplus$  indicates a quadratic sum.

The first term on the right-hand side is the "stochastic term" and depends on the fluctuations related to the physical development of the shower. The stochastic term in an homogeneous electromagnetic calorimeter is small, few percent in units of  $1/\sqrt{E(GeV)}$  because the energy deposited in the active volume by a monochromatic beam does not change event by event. In sampling calorimeters this is not the case, because the active layers are interleaved by absorber layers. These fluctuations, called "sampling fluctuation" represent the most important limitation in energy resolution in this type of calorimeters.

The second term, the "noise term", comes from the electronic noise of the readout chain and depends on the detector technique and on the electronics feature of the readout. Calorimeters in which the signal is collected in the form of light such as scintillators or homogeneous calorimeters, can have a small level of noise if a photosensitive device providing a high-gain multiplication of the signal is used as a first element of the readout. The noise will be larger in the detectors which collect the signal in charge form, using a preamplifier as a first element of the chain. In sampling calorimeters the signal to noise ratio can be improved increasing the sampling fraction (an higher sampling fraction implies a larger signal from the active medium).

The third term is the "constant term" and does not depend on the particle energy. It sums up effects caused by material non-uniformities, imperfections of mechanical structures, temperature gradients, radiation damage, etc. These effects can be cured, to a certain extent, by system calibrations. With the energy increase in the accelerators, this term becomes more and more important to the energy resolution. Typically, the constant term of an electromagnetic calorimeter should be around 1% or even smaller and this is particularly true for the homogeneous calorimeters because of the small stochastic term.

#### 3.3 Hadronic calorimeters

The first hadronic calorimeters were used by the end of the 1950s to study the cosmicray spectrum [58]. The energy E was assumed to be related to the hadronic shower multiplicity n(x) of fast charged particles versus the shower depth x through the specific ionization  $\epsilon$ , so that  $E = \epsilon \int n(x) dx$ . This estimation was correct within a factor of  $\simeq 2$ .

Nowadays, such detectors are built and optimized with a good understanding of the hadronic cascades also thanks to the development of Monte Carlo codes of the shower-ing processes [56, 59, 60].

#### 3.3.1 Hadronic cascade

Showers generated by strongly interacting particles are much more complex than electromagnetic showers. Few high energy particles are carrying half of the energy of the cascade while the other half goes into multi-particle production. The resulting shower is mostly made of nucleons and pions, of which about 1/3 are  $\pi^0$ . The parametrization of the longitudinal development of an hadronic shower is, as a consequence, more complex and the general form can be described by two terms: the first term corresponds to the electromagnetic energy deposition while the second to the hadronic energy deposition. Even if Monte Carlo algorithms provide good basis for electromagnetic shower simulations, there is no universal standard for the hadronic showers (more references can be found in [56]).

It is anyway possible to define the depth at which there is the maximum energy deposition in the hadronic shower:

$$t_{max}(\lambda_I) \approx [0.2ln(E) + 0.7],\tag{3.7}$$

where E is expressed in GeV,  $\lambda_I$  is the interaction length, and so the position of the shower maximum depends logarithmically on the energy. The 95% of a shower energy is contained in:

$$t_{95\%}(\lambda_I) \approx t_{max} + 2.5(E),$$

(3.8)

but since the fluctuations in energy deposition are very large, it is important to design a calorimeter with additional  $\sim 3\lambda_I$  of material [55].

#### 3.3.2 Energy resolution and compensation

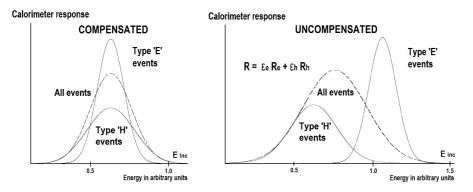

A fraction of the non-electromagnetic component of an hadronic shower mainly consists of the break of nucleon bindings and the kinetic energy of recoil nuclei that do not lead to a signal in the calorimeter. This is called invisible energy. As a result, on average it is expected to have, with the same incident energy, a lower response to hadrons respect to the electromagnetic shower. The invisible energy may represent a large part of the total non-electromagnetic energy with large event-to-event fluctuations [55].

The response to the electromagnetic energy deposition  $E_e$  can be characterized by a factor called *detector efficiency*  $\epsilon_e$  and the same for the hadronic part,  $E_h$  which is characterized by an efficiency  $\epsilon_h$ . In general,  $\epsilon_h < \epsilon_e$  because of the nucleon processes which do not yield visible energy, as explained before. The calorimeter response to hadronic shower can be describe by [55]:

$$R_h = E_h \epsilon_h + E_e \epsilon_e \tag{3.9}$$

As described in Figure 3.2, depending on the component with the major part of energy, the gap between the hadronic and electromagnetic detection efficiency will vary.

A calorimeter with equal response to both parts would improve the situation. This type of calorimeters are called "compensated" and are characterized by  $\epsilon_e/\epsilon_h = 1$ . Compensated calorimeters have no gap between electromagnetic and hadronic components, while for non-compensated calorimeters the gap is present. The larger this gap is, the wider the spread for the detected energy will be. In the figure the response for electromagnetic events ("Type E events") and the response for hadronic events ("Type H events") are indicated with solid line, while the overall calorimeter response ("all events") is drawn with the dashed line.

Figure 3.2: Calorimeter compensated response (left) and not compensated response (right) [55].

### 3.4 Structure of ATLAS calorimeters

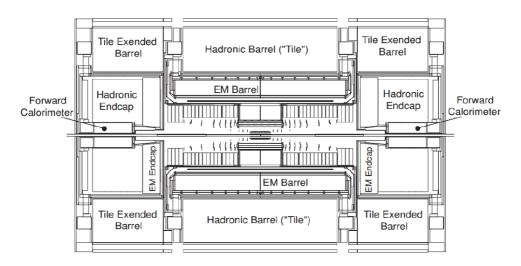

The ATLAS calorimetry system consists of an electromagnetic calorimeter covering the pseudorapidity region  $|\eta| < 3.2$ , a hadronic barrel calorimeter covering  $|\eta| < 1.7$ , hadronic end-cap calorimeters covering  $1.5 < |\eta| < 3.2$ , and forward calorimeters covering  $3.1 < |\eta| < 4.9$ .

A two-dimensional view of both electromagnetic and hadronic calorimeters is shown in Figure 3.3 (more details can be found in Sections 2.3 and 3.5). All calorimeters used in ATLAS are sampling calorimeters.

Figure 3.3: 2D view of the ATLAS calorimeters, LAr and Tile [35].

The electromagnetic calorimeter has in addition a presampler detector over the pseudorapidity range  $|\eta| < 1.8$ , installed immediately behind the cryostat cold wall, and used to correct for the energy lost in the material upstream of the calorimeter [35].

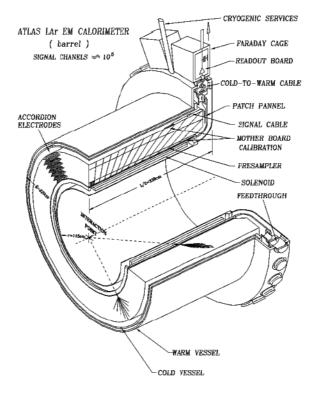

The barrel electromagnetic calorimeter is contained in a barrel cryostat, shown in Figure 3.4, which surrounds the inner detector cavity. The solenoid which supplies the 2 T magnetic field to the inner detector is integrated into the vacuum of the barrel cryostat

and is placed in between the tracker and the electromagnetic calorimeter. Two end-cap cryostats house the end-cap electromagnetic and hadronic calorimeters, as well as the forward calorimeters.

Figure 3.4: Barrel cryostat [35].

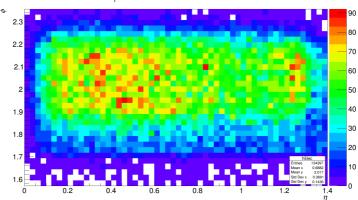

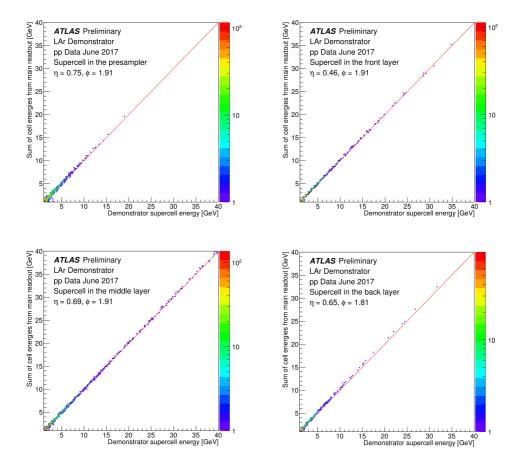

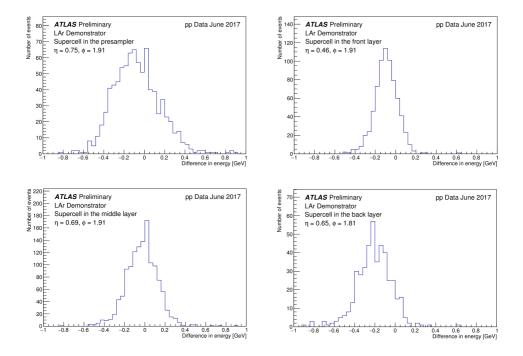

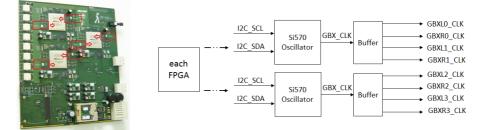

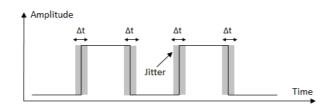

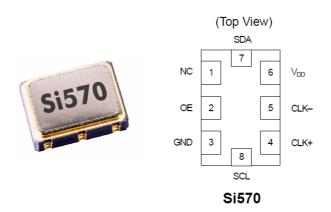

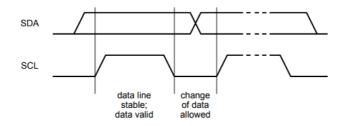

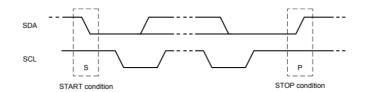

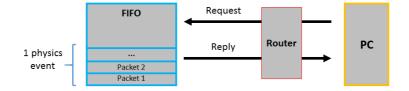

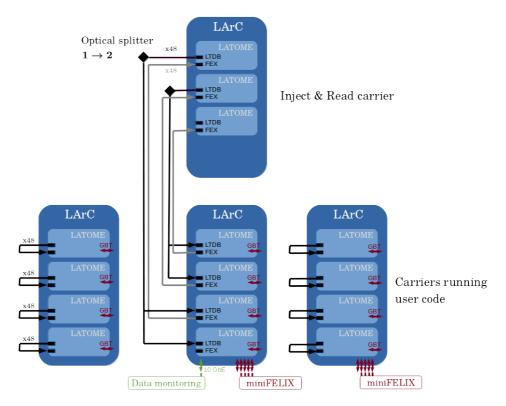

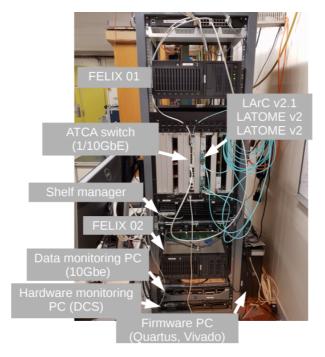

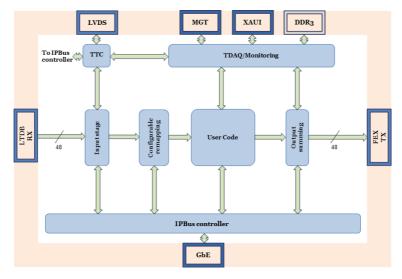

## 3.5 LAr ATLAS Calorimeter