Available online at www.sciencedirect.com

Electronic Notes in Theoretical Computer Science

Electronic Notes in Theoretical Computer Science 153 (2006) 23-33

www.elsevier.com/locate/entcs

# ESBC: an application for computing stabilization bounds

## Alessandro Avellone<sup>a</sup> Mauro Ferrari<sup>b,1</sup> Camillo Fiorentini<sup>c</sup> Guido Fiorino<sup>a</sup> Ugo Moscato<sup>a</sup>

<sup>a</sup> Dipartimento di Metodi Quantitativi per le Scienze Economiche Aziendali, Università Milano-Bicocca, piazza dell'Ateneo Nuovo 1, 20126 Milano, Italy

<sup>b</sup> Dipartimento di Informatica e Comunicazione, Università degli Studi dell'Insubria, via Mazzini 5, 21100 Varese, Italy

<sup>c</sup> Dipartimento di Scienze dell'Informazione, Università degli Studi di Milano, via Comelico 39, 20135 Milano, Italy

#### Abstract

We describe the application ESBC to perform the timing analysis of a combinatorial circuit. The circuit is described by formulas of Classical Logic and the delays of propagation of the signals in a gate are represented by a kind of valuation form semantics. ESBC computes the exact stabilization times at which the output signals stabilize.

Keywords: Valuation form semantics, timing analysis, intermediate logics

### 1 Introduction

Valuation forms provide an intensional semantics of formulas inspired to the BHK explanation of constructive connectives (see e.g., [3,8]). Roughly speaking, a valuation form for a formula A is an "object" providing a *constructive justification* for the truth of A. In recent years, several families of valuation forms have been devised to formalize different problems in logic and computer science. As an example we cite [6] where valuation forms are studied from a purely logical point of view; [5] where they are used to formalize databases;

<sup>&</sup>lt;sup>1</sup> Contacting author: mauro.ferrari@uninsubria.it.

[4] where valuation forms characterize stabilization bounds in combinatorial circuits and [7] where valuation forms provide the semantics of CML, a Constructive Modeling Language for Object Oriented systems.

One of the interesting aspects of valuation forms is that they are compatible with classical semantics. In the framework of formal methods one can use formulas with the intended classical meaning to formalize the system at hand and valuation forms to characterize some intensional property of the system. As an example, in the context of timing analysis formulas describe the usual functional behavior of the circuit components while valuation forms are the functions describing the delays of the circuit components. We remark that in this context valuation forms provide a *partial* semantical justification of the truth of the formulas since they only characterize the correctness of the circuit up to stabilization bounds.

All the above mentioned families of valuation forms characterize constructive superintuitionistic logics with constructive negation and any of these logics is a superset of the logic **E** studied in [6]. This means that the natural deduction calculus ND<sub>E</sub> for logic **E** devised in [6] is valid for all these semantics. This allows us to define a parametric extraction procedure that, selected the family of valuation forms of interest, extracts from an ND<sub>E</sub> proof of  $A_1, \ldots, A_n \vdash B$ a function computing the valuation form justifying B, having as inputs the valuation forms for  $A_1, \ldots, A_n$ .

In this paper we describe the stabilization bound semantics and an application built to compute and evaluate the valuation forms describing stabilization bounds of combinatorial circuits. This application consists of a C++ theorem prover for the propositional logic **E** based on tableau calculi (fully described in [1]), a Java package translating tableau proofs into ND<sub>E</sub> proofs, a Java package extracting the function computing the stabilization bound from a correctness ND<sub>E</sub>-proof of the circuit and the Java package which evaluates the function.

The paper is structured as follows: in Section 2 we discuss the stabilization bounds semantics, in Section 3 we briefly describe the tableau calculus, the theorem prover and the translation into  $ND_{\mathbf{E}}$ -proofs and finally in Section 4 we describe the implementation of the valuation form extractor and provide an example.

#### 2 Exact Stabilization Bounds

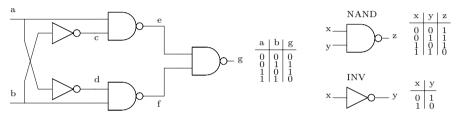

In the logical approach to circuit analysis a semantics represents an abstraction from the physical details. To give an example, let us consider the gates INV and NAND of Figure 1. Their behavior is specified by the following formulas of classical logic

$$INV(x, y) \equiv (x \to \sim y) \land (\sim x \to y)$$

$$NAND(x, y, z) \equiv (x \land y \to \sim z) \land (\sim x \lor \sim y \to z)$$

Indeed, the truth table of INV(x, y) represents the input/output behavior of the INV gate having x as input and y as output. Analogously, NAND(x,y,z) represents the NAND gate, where x and y are the inputs and z is the output. Similarly, the classical behavior of the XOR circuit can be specified by the formula

$$\operatorname{XOR}(x, y, z) \equiv ((x \land \sim y) \lor (\sim x \land y) \to z) \land ((x \land y) \lor (\sim x \land \sim y) \to \sim z)$$

where x and y represent the inputs and z the output.

Fig. 1. The XOR circuit and its components

Classical semantics allows us to study the input/output behavior of combinatorial circuits, but does not allow us to represent temporal information about the stabilization properties of the circuits. A more realistic description of the XOR circuit of Figure 1 should consider the instant at which the signals become stable and the delays in the propagation of signals; e.g., an "informal" characterization of the behavior of the above circuit should be as follows:

| (a stable to 1 at $t_1$ ) and (b stable to 0 at $t_2$ )<br>or<br>(a stable to 0 at $t_1$ ) and (b stable to 1 at $t_2$ ) | $\Rightarrow$ | $(g \text{ stable to 1 at } F(t_1, t_2))$          |

|--------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------|

| (a stable to 1 at $t_1$ ) and (b stable to 1 at $t_2$ )<br>or<br>(a stable to 0 at $t_1$ ) and (b stable to 0 at $t_2$ ) | $\Rightarrow$ | $(g \text{ stable to } 0 \text{ at } G(t_1, t_2))$ |

where F and G are functions from  $\mathbf{N}^2$  to  $\mathbf{N}$  and  $\mathbf{N}$  represents discrete time.

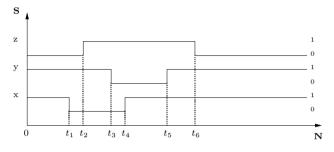

To formalize these aspects, we recall the main notions introduced in [4]. A signal is a discrete timed boolean function  $\sigma \in \mathbf{N} \to \mathbf{B}$ . A circuit is characterized by a set of observables  $\mathbf{S} = \{a, b, c_1, c_2, ...\}$  (the atomic formulas of our language); for instance, to represent the XOR circuit of Figure 1, we need the set of observables  $\{a, b, c, d, e, f, g\}$  representing the connections between the gates of the circuit. A waveform is a map  $V \in \mathbf{S} \to (\mathbf{N} \to \mathbf{B})$  associating with every observable a signal. A waveform represents an observable property of a circuit C, whereas an observable behavior of C is described by a set of waveforms. A signal V(a) is stable to 1 at time t iff V(a)(k) = 1 for all  $k \ge t$ ; similarly, V(a) is stable to 0 at t iff V(a)(k) = 0 for all  $k \ge t$ . We only consider eventually stable waveforms V, namely: for every  $a \in \mathbf{S}$ , there is t such that the signal V(a) is stable at time t (to 0 or to 1). Figure 2 describes a possible eventually stable waveform for the NAND circuit. Here, the input signal V(x)stabilizes to 1 at time  $t_4$ , while the input signal V(y) stabilizes to 1 at time  $t_5$ ; the output signal V(z) stabilizes to 0 at time  $t_6$ , with a certain delay with respect to the time  $t_5$  where both the inputs are stable to 1.

Fig. 2. A waveform for NAND

To express stabilization properties of waveforms and behaviors we use a propositional language  $\mathcal{L}_{\mathbf{S}}$  based on a denumerable set of observables **S**. Formulas of  $\mathcal{L}_{\mathbf{S}}$  are inductively defined as follows: for every  $a \in \mathbf{S}$ , a is an atomic formula of  $\mathcal{L}_{\mathbf{S}}$ ; if  $A, B \in \mathcal{L}_{\mathbf{S}}$ , then  $A \wedge B, A \vee B, A \to B$  and  $\sim A$  belong to  $\mathcal{L}_{\mathbf{S}}$ . Temporal information is represented by stabilization bounds which is a variant of the valuation form semantics introduced in [6]. Let A be a formula of  $\mathcal{L}_{\mathbf{S}}$ ; the set of stabilization bounds  $\lceil A \rceil$  for A is inductively defined on the structure of A as follows:

- If A = a or  $A = \sim a$ , with  $a \in \mathbf{S}$ , then  $\lceil A \rceil = \mathbf{N}$ .

- $\lceil B \land C \rceil = \lceil B \rceil \times \lceil C \rceil$ .

•

$$\lceil A_1 \lor A_2 \rceil = \lceil A_1 \rceil \oplus \lceil A_2 \rceil = \{(i, \alpha_i) \mid i \in \{1, 2\} \text{ and } \alpha_i \in \lceil A_i \rceil\}$$

- $\lceil B \to C \rceil = \{ f \mid f : \lceil B \rceil \to \lceil C \rceil \}.$

- $\lceil \sim (A_1 \land A_2) \rceil = \lceil \sim A_1 \rceil \oplus \lceil \sim A_2 \rceil = \{(i, \alpha_i) \mid i \in \{1, 2\} \text{ and } \alpha_i \in \lceil \sim A_i \rceil\}.$

- $\lceil \sim (B \lor C) \rceil = \lceil \sim B \rceil \times \lceil \sim C \rceil$ .

- $\lceil \sim (B \to C) \rceil = \lceil B \rceil \times \lceil \sim C \rceil.$

- $\lceil \sim B \rceil = \lceil B \rceil$ .

Intuitively, a stabilization bound  $\alpha \in \lceil A \rceil$  intensionally represents a set of waveforms that validate A for the "same reasons" and with the "same delay bounds". The main concern of timing analysis is to determine the *exact*  time instant where an output signal of a circuit becomes stable, and this is performed by computing exact stabilization bounds. Let A be a formula, let  $\alpha \in [A]$  and let V be an eventually stable waveform;  $\alpha$  is exact for V and A if one of the following conditions holds:

- A = a and  $\alpha = \min\{t \mid V(a) \text{ is stable to 1 at } t\}.$

- $A = \sim a$  and  $\alpha = \min\{t \mid V(a) \text{ is stable to } 0 \text{ at } t\}$ .

- $A = B \wedge C$ ,  $\alpha = (\beta, \gamma)$ ,  $\beta$  is exact for B and V, and  $\gamma$  is exact for C and V.

- $A = B_1 \vee B_2$ ,  $\alpha = (i, \beta_i)$ , with  $i \in \{1, 2\}$ , and  $\beta_i$  is exact for V and  $B_i$ .

- $A = B \to C$  and, for all  $\beta \in \lceil B \rceil$ , if  $\beta$  is exact for V and B, then  $\alpha(\beta)$  is exact for V and C.

- $A = \sim (B_1 \wedge B_2), \alpha = (i, \beta_i)$ , with  $i \in \{1, 2\}$ , and  $\beta_i$  is exact for V and  $\sim B_i$ .

- $A = \sim (B \lor C)$ ,  $\alpha = (\beta, \gamma)$ ,  $\beta$  is exact for V and  $\sim B$ ,  $\gamma$  is exact for V and  $\sim C$ .

- $A = \sim (B \to C), \ \alpha = (\beta, \gamma), \ \beta$  is exact for V and B,  $\gamma$  is exact for V and  $\sim C$ .

- $A = \sim B$  and  $\alpha$  is exact for V and B.

To give an example, let us consider the above INV and NAND gates. A stabilization bound for INV(x, y) is a pair of functions from **N** to **N**. Let us assume that the INV gate has the following observable behavior: if the signal V(x) stabilizes to 1 at t, then the signal V(y) stabilizes to 0 at  $t + \delta_0$ ; if V(x) stabilizes to 0 at t, then V(y) stabilizes to 1 at  $t + \delta_1$ . In our semantical framework, this is described by the exact stabilization bound  $(f_{INV}^-, f_{INV}^+)$  for V and INV(x, y) defined as follows:

$$f_{\text{INV}}^{-}(t) = t + \delta_0 \qquad f_{\text{INV}}^{+}(t) = t + \delta_1$$

Similarly, a stabilization bound for NAND(x, y, z) is a pair of functions

$$f_{\mathrm{NAND}}^-: \mathbf{N} imes \mathbf{N} o \mathbf{N} \qquad f_{\mathrm{NAND}}^+: \mathbf{N} \oplus \mathbf{N} o \mathbf{N}$$

An exact stabilization bound  $(f_{\text{NAND}}^-, f_{\text{NAND}}^+)$  for the waveform V of Figure 2 and NAND(x, y, z) must satisfy

$$f_{\text{NAND}}^{-}((t_4, t_5)) = t_6$$

which formalizes the fact that, if V(x) stabilizes to 1 at  $t_4$  and V(y) stabilizes to 1 at  $t_5$ , then V(z) stabilizes to 0 at  $t_6$ .

To give a picture of our extraction algorithm, let C be a circuit consisting of the gates  $G_1, \ldots, G_n$ , where each  $G_i$  is described by a formula  $A_i$ , and let B

| $\frac{\sim A_i}{\sim (A_1 \wedge A_2)} \operatorname{I}_{\sim \wedge_i} i \in \{1,2\}$                                                                          | $\sim (A \wedge B)$                                                                                                                                                     | $\begin{bmatrix} \sim A \end{bmatrix} \qquad \begin{bmatrix} \sim B \end{bmatrix}$ $\vdots \\ \pi_1 \qquad \vdots \\ C \qquad C \qquad C$ |                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| $\frac{A}{\sim A} \stackrel{I \sim}{\longrightarrow} \frac{A}{A} \stackrel{E \sim}{\longrightarrow} \frac{A}{\sim (A \to B)} \stackrel{I \sim}{\longrightarrow}$ | $\frac{\overline{A} \sim A}{\sim (A \lor B)} \stackrel{I \sim \vee}{\longrightarrow} \frac{(A \lor B)}{A} \stackrel{E \sim \rightarrow_1}{\longrightarrow} \frac{A}{A}$ | $ \frac{C}{\sim (A_1 \lor A_2)} \\ \frac{A_i}{\sim A_i} \\ \frac{\sim (A \to B)}{\sim B} \\ \xrightarrow{F} \\ F $                        | $E{\sim}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

$\begin{array}{c} {\rm Table \ 1} \\ {\rm The \ negation \ rules \ of \ the \ calculus \ ND_{\bf E}} \end{array}$

be the formula describing the input/output behavior of C (see the examples above). A formal correctness verification of the circuit amounts to providing a classical proof  $\pi : A_1, \ldots, A_n \vdash B$ , where  $A_1, \ldots, A_n$  are the open assumptions of  $\pi$  and B is the proved formula. Moreover, let  $V_i$   $(1 \leq i \leq n)$  be the waveform corresponding to the observable behavior of  $G_i$  and let  $\alpha_i$  be an exact stabilization bound for  $A_i$  and  $V_i$  (namely,  $\alpha_i$  describes the behavior of  $G_i$ ); finally, let V be the waveform corresponding to the observable behavior of C (V describes the temporal information about the input/output signals of the whole circuit). To determine V, it suffices to compute an exact stabilization bound for V and B. As fully described in [4], this can be accomplished by considering proofs of the constructive calculus ND<sub>E</sub> obtained by adding to the usual natural deduction calculus for intuitionistic logic the rules of Table 1, where we put between square brackets the discharged assumptions.

As a matter of fact, the main result of [4] states:

**Theorem 2.1** Let  $\pi : A_1, \ldots, A_n \vdash B$  be a proof of the calculus ND<sub>E</sub>. There is a recursive function  $F_{\pi} : \lceil A_1 \rceil \times \cdots \times \lceil A_n \rceil \rightarrow \lceil B \rceil$  such that, for all  $\alpha_1 \in \lceil A_1 \rceil$ ,  $\ldots, \alpha_n \in \lceil A_n \rceil$  and for every eventually stable waveform V, if  $\alpha_1$  is an exact stabilization bound for V and  $A_1, \ldots, \alpha_n$  is an exact stabilization bound for V and  $A_n$ , then  $F_{\pi}(\alpha_1, \ldots, \alpha_n)$  is an exact stabilization bound for V and B.

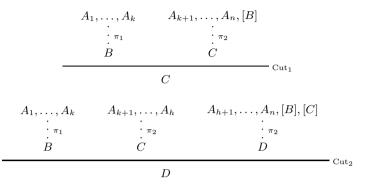

The function  $F_{\pi}$  is defined according to the structure of  $\pi$ . Here we only provide some cases. If  $\pi : A \vdash A$  only consists of an assumption introduction,  $F_{\pi}$  is the identity function. If  $\pi$  is the proof

28

$B \wedge C$

then  $F_{\pi}(\underline{\alpha}) = (F_{\pi_1}(\alpha_1, \dots, \alpha_k), F_{\pi_2}(\alpha_{k+1}, \dots, \alpha_n)).$

If  $\pi$  terminates with an implication introduction

$$\begin{array}{c} A_1, \dots, A_n, [B] \\ \vdots \\ \pi_1 \\ C \\ \hline \\ B \to C \end{array} \to 1$$

then  $F_{\pi}(\underline{\alpha})$  is the function  $f: \lceil B \rceil \to \lceil C \rceil$  such that  $f(\beta) = F_{\pi_1}(\underline{\alpha}, \beta)$ . If  $\pi$  is the proof

$$\begin{array}{ccc} A_1, \dots, A_k & A_{k+1}, \dots, A_n \\ \vdots & \vdots & \vdots \\ B & B \rightarrow C \\ \hline C & \\ \end{array} \xrightarrow{} E \\ \end{array} \xrightarrow{} E \\ C \\ \end{array}$$

then  $F_{\pi}(\underline{\alpha}) = F_{\pi_2}(\alpha_{k+1}, \dots, \alpha_n)(F_{\pi_1}(\alpha_1, \dots, \alpha_k)).$

#### 3 Building NDE proofs

To apply our extraction procedure, we need a  $ND_E$  proof of correctness of the circuit. However, it is well-known that natural deduction calculi are not adequate for proof search. For this reason we use a tableau based theorem prover to build up the correctness proof and then we translate it into a  $ND_E$  proof. In this section we give a quick overview of both the tableau calculus and the translation rules.

Our theorem prover implements the tableau calculus TAB of [1] which has the "same deductive power" of  $ND_E$ . Differently from natural deduction, tableaux are goal-oriented calculi; this feature makes them suitable for automated deduction (see [2] for an account of the wide of applicability of tableau systems).

The tableau calculus TAB uses an object language with the signs  $\mathbf{T}$ ,  $\mathbf{F}$ ,  $\mathbf{F_c}$  and  $\mathbf{T_c}$  and is equivalent to ND<sub>E</sub> in the following sense:

•  $\pi : A_1, \ldots, A_n \vdash B \in ND_E$  iff there exists a tableau proof in TAB of  $\{TA_1, \ldots, TA_n, FB\}$ .

The depth of every proof table is linearly bounded by the length of the input formulas, moreover there exists an "efficient" strategy in the application of the rules which strongly bounds the backtracking. The theorem prover described in [1] implements an  $O(n^2)$ -SPACE proof search procedure for proofs of TAB.

To simplify the translation from tableau proofs into natural deduction

proofs, we add to the calculus  $ND_{\mathbf{E}}$  the following cut-rules

Here we give two examples of translation. Let  $\Gamma = \{H_1, \ldots, H_n\}$  and let  $S = \{\mathbf{T}H_1, \dots, \mathbf{T}H_n\}.$ The rule  $\frac{S, \mathbf{F}C, \mathbf{T}(A \wedge B)}{S, \mathbf{F}C, \mathbf{T}A, \mathbf{T}B} \mathbf{T} \wedge$ , is translated as

$$\frac{A \wedge B}{A} \xrightarrow{E \wedge_{1}} \frac{A \wedge B}{B} \xrightarrow{E \wedge_{2}} \begin{array}{c} \Gamma, [A], [B] \\ \vdots \\ \pi \\ C \end{array} \xrightarrow{C} C$$

The rule  $\frac{S, \mathbf{F}D, \mathbf{T}(A \land B \to C)}{S, \mathbf{F}D, \mathbf{T}(A \to (B \to C))} \mathbf{T} \to \wedge$  is translated as

In the above proofs, the number beside the rule name indicate the points where the assumptions are discharged.

The translation of the proof generated by the tableau theorem prover (implemented in C++ language) is performed by a JAVA package of the application.

#### The system ESBC $\mathbf{4}$

In this section we discuss the implementation issues. The system software ESBC performs all the steps to compute stabilization bounds of combinatorial circuits discussed in the previous sections. It consists of the following independent modules: (i) the tableau theorem prover, (ii) the translator from proofs of TAB into proofs of ND<sub>E</sub>, (iii) the tool which computes stabilization bounds exploiting proofs produced by (ii).

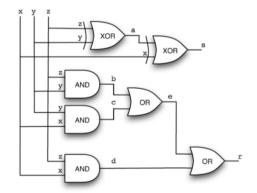

As a summarizing example, let us consider the Full Adder Circuit of Figure 3. The gates in the circuit are represented by the formulas in the set:

$$\mathcal{C} = \{ \text{XOR}(y, z, a), \text{XOR}(a, x, s), \text{AND}(y, z, b), \text{AND}(x, y, c), \\ \text{AND}(x, z, d), \text{OR}(b, c, e), \text{OR}(e, d, r) \}$$

The behavior of AND, OR and XOR gates are specified by the formulas:

$$\begin{split} &\operatorname{AND}(x, y, z) \equiv (x \land y \to z) \land (\sim x \lor \sim y \to \sim z) \\ &\operatorname{OR}(x, y, z) \equiv (\sim x \land \sim y \to \sim z) \land (x \lor y \to z) \\ &\operatorname{XOR}(x, y, z) \equiv ((x \land \sim y) \lor (\sim x \land y) \to z) \land ((x \land y) \lor (\sim x \land \sim y) \to \sim z) \end{split}$$

The input/output behavior of the signals of the circuit is specified by the formula:

$$S \equiv (\sim x \land \sim y \land \sim z \to \sim s \land \sim r) \land (\sim x \land \sim y \land z \to s \land \sim r) \land (\sim x \land y \land z \to s \land \sim r) \land (\sim x \land y \land z \to \sim s \land r) \land (x \land \sim y \land \sim z \to s \land \sim r) \land (x \land \sim y \land z \to \sim s \land r) \land (x \land y \land \sim z \to \sim s \land r) \land (x \land y \land z \to \sim s \land r) \land (x \land y \land z \to \sim s \land r) \land$$

Fig. 3. The Full Adder Circuit

Firstly, we search for a proof  $\pi : \mathcal{C} \vdash S$  of  $ND_{\mathbf{E}}$ , by using modules (i) and (ii) of ESBC. Then, (iii) uses  $\pi$  to compute stabilization bounds of the circuit. We have to provide the stabilization bound of the elementary gates. As discussed in Section 2, a stabilization bound for AND(x, y, z) is a pair of functions  $(f_{AND}^-, f_{AND}^+)$ , where

$$f_{AND}^-: \mathbf{N} \oplus \mathbf{N} \to \mathbf{N} \qquad f_{AND}^+: \mathbf{N} \times \mathbf{N} \to \mathbf{N}$$

Let us assume that the output signal of the AND gate stabilizes to 1 with delay 2 after the stabilization to 1 of both the input signals and that it stabilizes to 0 with delay 5 after the stabilization to 0 of either of the input signals. Then, we have to set

$$f_{\text{AND}}^{-}(i,t) = t + 5$$

$f_{\text{AND}}^{+}(t_1,t_2) = max\{t_1,t_2\} + 2, i \in \{1,2\}$

Similarly, a stabilization bound for OR(x, y, z) is a pair of functions  $(f_{OR}^-, f_{OR}^+)$ , where

$$f_{\mathrm{OR}}^-: \mathbf{N} imes \mathbf{N} o \mathbf{N} \qquad f_{\mathrm{OR}}^+: \mathbf{N} \oplus \mathbf{N} o \mathbf{N}$$

We assume that behavior of OR gate corresponds to the following exact stabilization bound:

$$f_{\rm OR}^-(t_1, t_2) = max\{t_1, t_2\} + 6 \qquad f_{\rm OR}^+(i, t) = t + 10, \quad i \in \{1, 2\}$$

Finally, a stabilization bound for XOR(x, y, z) is a pair of functions  $(f_{XOR}^-, f_{XOR}^+)$ , where

$$f_{\mathrm{XOR}}^-: (\mathbf{N} imes \mathbf{N}) \oplus (\mathbf{N} imes \mathbf{N}) o \mathbf{N} \qquad f_{\mathrm{XOR}}^+: (\mathbf{N} imes \mathbf{N}) \oplus (\mathbf{N} imes \mathbf{N}) o \mathbf{N}$$

We choose  $f_{\text{XOR}}^-$  and  $f_{\text{XOR}}^+$  as follows:

$$f_{\text{XOR}}^{-}(i,(t_1,t_2)) = max\{t_1,t_2\} + 1, \quad i \in \{1,2\}$$

$$f_{\text{XOR}}^{+}(i,(t_1,t_2)) = max\{t_1,t_2\} + 5, \quad i \in \{1,2\}$$

We compute the exact stabilization bounds of output signals assuming that input signals are stable at time 0. By applying the above exact stabilization bounds to the function  $F_{\pi}$  associated with  $\pi$ , ESBC produces the results given in the following table where for every input we put in evidence the truth value of the signal and for every output both the truth value and the stabilization bounds are provided. For instance, if the signals V(x), V(y) and V(z) stabilizes to 1 at time 0, we have that V(s) stabilizes to 1 at time 6 and V(r)stabilizes to 1 at time 12 (see the last row of the table).

| x                                                       | У                                                                | z                                                                | S                                                                                      | r                                                                                           |

|---------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| false<br>false<br>false<br>true<br>true<br>true<br>true | false<br>false<br>true<br>true<br>false<br>false<br>true<br>true | false<br>true<br>false<br>true<br>false<br>true<br>false<br>true | (false,10)<br>(true,2)<br>(false,10)<br>(true,6)<br>(false,6)<br>(false,6)<br>(true,6) | (false,17)<br>(false,17)<br>(false,17)<br>(true,22)<br>(false,17)<br>(true,12)<br>(true,12) |

|                                                         |                                                                  |                                                                  | (,-,                                                                                   | (;)                                                                                         |

#### References

- A. Avellone, C. Fiorentini, G. Fiorino, and U. Moscato. A space efficient implementation of a tableau calculus for a logic with a constructive negation. In J. Marcinkowski and A. Tarlecki, editors, *Computer Science Logic, 18th International Workshop, CSL 2004*, volume 3210 of *Lecture Notes in Computer Science*, pages 488–502, 2004.

- [2] M. D'Agostino, D.M. Gabbay, R. Hähnle, and J. Posegga, editors. Handbook of tableau methods. Kluwer Academic Press, 1999.

- [3] M.A.E. Dummett. Elements of Intuitionism. Claredon Press, Oxford, 1977.

- [4] M. Ferrari, C. Fiorentini, and M. Ornaghi. Extracting exact time bounds from logical proofs. In A. Pettorossi, editor, *Logic Based Program Synthesis and Transformation*, 11th International Workshop, LOPSTR 2001, Selected Papers, volume 2372 of Lecture Notes in Computer Science, pages 245–265. Springer-Verlag, 2002.

- [5] P. Miglioli, U. Moscato, and M. Ornaghi. A constructive logic approach to database theory. In Logic Programming-Proceeding of the First Russian Conference on Logic Programming, pages 302–321, 1990.

- [6] P. Miglioli, U. Moscato, M. Ornaghi, S. Quazza, and G. Usberti. Some results on intermediate constructive logics. Notre Dame Journal of Formal Logic, 30(4):543–562, 1989.

- [7] M. Ornaghi, M. Benini, M. Ferrari, C. Fiorentini, and A. Momigliano. A constructive modeling language for object oriented information systems. *CLASE*, 2005.

- [8] A.S. Troelstra. Aspects of constructive mathematics. In J. Barwise, editor, Handbook of Mathematical Logic. North-Holland, 1977.