# Novel qutrit circuit design for multiplexer, De-multiplexer, and decoder

Asma Taheri Monfared<sup>1</sup>  $\cdot$  Valentina Ciriani<sup>1</sup>  $\cdot$  Lauri Kettunen<sup>2</sup>  $\cdot$  Majid Haghparast<sup>2</sup>

Received: 14 May 2022 / Accepted: 24 November 2022 / Published online: 9 December 2022 © The Author(s) 2022

# Abstract

Designing conventional circuits present many challenges, including minimizing internal power dissipation. An approach to overcoming this problem is utilizing quantum technology, which has attracted significant attention as an alternative to Nanoscale CMOS technology. The reduction of energy dissipation makes quantum circuits an up-and-coming emerging technology. Ternary logic can potentially diminish the quantum circuit width, which is currently a limitation in quantum technologies. Using qutrit instead of qubit could play an essential role in the future of quantum computing. First, we propose two approaches for quantum ternary decoder circuit in this context. Then, we propose a quantum ternary multiplexer and quantum ternary demultiplexer to exploit the constructed quantum ternary decoder circuit. Techniques to achieve lower quantum cost are of importance. We considered two types of circuits, one in which the output states are always restored to the initial input states and the other in which the states of the output are irrelevant. We compare the proposed quantum ternary circuits with their existing counterparts and present the improvements. It is possible to realize the proposed designs using macro-level ternary gates that are based on the ion-trap realizable ternary 2-qutrit Muthukrishnan-Stroud and 1-qutrit permutation gates.

Keywords Quantum computing  $\cdot$  Qutrit  $\cdot$  Quantum ternary logic  $\cdot$  Restoration technique  $\cdot$  Non-restoration technique

# **1** Introduction

According to Moore's law, computer processing power has steadily increased in the last few decades owing to the escalating transistor density on chips. To reduce the width and

Majid Haghparast majid.m.haghparast@jyu.fi

<sup>&</sup>lt;sup>1</sup> Dipartimento di Informatica, Università degli Studi di Milano, Milano, Italy

<sup>&</sup>lt;sup>2</sup> Faculty of Information Technology, University of Jyväskylä, P.O.Box 35, 40014 Jyväskylä, Finland

increase the number of transistors, the problem of electron interaction and the creation of unwanted capacitors should be considered [1, 2]. It will eventually be impossible to keep downsizing the current technology forever since this will eventually reach the fundamental physical limits of atomic structures. Rolf Landauer demonstrated that losing every bit of information in irreversible conventional circuits leads to an internal power dissipation of at least kTln2 Joules, where T is the absolute temperature of the environment and k is the Boltzmann constant [3]. Scientists have sought alternatives to CMOS technology due to a growing demand for lower power consumption and higher processing power [4].

It is believed that quantum computing has a great deal of potential to parallelize information processing. In quantum computing, quantum mechanical systems are used to process quantum information. Various quantum technologies have been introduced in the literature: ion trap systems in which information is represented as the energy levels of individual ions; optical quantum systems, which represent information using different polarizations of photons; silicon NMR systems where information stored in the spin of the nucleus of an atom or superconductor [5–10].

The quantum computer is a promising candidate for the next generation of computers, which are more powerful than classical ones. They are believed to solve intractable problems that the current classical computers cannot solve. Since quantum computing is inherently reversible and information is not lost in reversible computations, the use of quantum gates prevents power dissipation [11, 12]. Quantum gates implement permutation functions and have the same number of outputs and inputs [13–16]. Fan-out and feedback from output to input are prohibited when designing quantum reversible circuits [17]. The research on quantum computers is moving towards avoiding energy loss and designing computers with high speed [11].

Qudit circuits and more specifically qutrit ones in quantum technology are recently investigated by researchers due to their advantages over their binary counterparts, including logarithmic reductions in the number of qudits [10, 50–52]. For a Hilbert space of N dimensions, in a quantum binary system, the required number of qubits is equal to [18–20]:

$$n_2 = \log_2 N \tag{1}$$

However, in a quantum 3-valued system, the required number of qudits is:

$$n_3 = \log_3 N \tag{2}$$

$$n_3 = \log_3 N = \frac{\log_2 N}{\log_2 3} = \frac{n_2}{\log_2 3} = \left(\frac{1}{\log_2 3}\right)n_2 = \frac{1}{1.585}n_2 = 0.63n_2 \quad (3)$$

As can be seen in Eq. (3), a 3-valued quantum system requires 0.63 times the memory of the respective binary quantum system. Therefore, logarithmic reduction in the number of qudits can be considered the main advantage of a 3-valued quantum system over a binary quantum system [18–20].

From the points discussed above, it can be concluded that in quantum ternary systems, 0.37 times fewer qutrits are required than the required qubits in the quantum

binary systems [18-20]. In this work, we will focus on qutrit systems. Compared to qubit systems, gutrit systems simplify the decomposition and reduce resources, requiring fewer qubits and less memory. Investigating qutrit systems are essential since we have access to a limited number of qudits. However, the preparation, control, accessibility, fault tolerance, runtime, reliability, noise, and error rate issues, which are difficult to surmount, also need to be investigated. Since using qutrit systems, a smaller amount of energy separates states beyond zero and one; hence noise and control issues become challenging. An inverse engineering method is proposed in [58] for the dynamical control of three-level open systems by considering energy relaxation and dephasing. This paper shows that by using a superconducting qutrit platform, the error rate of the controls is significantly reduced. Authors in [51] discussed constructing any qutrit multiple-controlled Clifford + T unitary using just Clifford + T gates and without using any ancilla lines. They proposed ancilla-free Clifford + T implementations of multiple-controlled T gates as well as all versions of qutrit multiple-controlled Toffoli gate, while the analogous results for qubits are impossible [51]. An implementation of ternary classical reversible functions on n-trits as an ancilla-free qutrit unitary is also provided in [51]. Quantum systems are highly sensitive to errors, and it is even possible for a state to be changed when interacting with the environment [57, 62]. In [62], an error-correcting code is proposed which can correct a single error in a qutrit. Fault tolerance in quantum circuits can be determined by the entangling gate and the interaction network topology [59]. It is important to optimize the number of quantum units as well as the depth of a quantum circuit in order to minimize the effect of noise in the output. The authors in [61] discussed the advantages of using qutrit systems instead of qubit systems in scalar quantum electrodynamics. In [60], qutrit systems were shown to outperform qubits in terms of reliability and runtime.

Any combinational logic circuit can be implemented in a binary system using multiplexers and basic logic gates, which is also true for ternary logic [53]. Many quantum ternary circuits implementation for different types of computational units of quantum systems, including full adder, half adder, parallel adder/subtractor, subtractor, multiplier, decoder, encoder, demultiplexer, and multiplexer, can be found in the literature [20–31, 57]. Decoder, multiplexer, and demultiplexer circuits are major sub-circuits needed for constructing ternary quantum oracles and ternary system designs such as communication systems, computer memory, and arithmetic logic unit [54]. In [31], a quantum ternary decoder with a quantum cost of 57 is presented.

Moreover, quantum ternary multiplexer and demultiplexer are introduced in [30], with a quantum cost of 102. This paper focuses on synthesizing more efficient quantum ternary decoders, multiplexers, and demultiplexers compared to existing designs in [30, 31]. Moreover, we present the characteristics of the proposed circuits with respect to quantum cost, depth, number of garbage outputs, and number of constant inputs. The synthesized circuits are usually evaluated by minimizing these important parameters, which leads to better efficiency of the quantum ternary logic design [32–34]. In the literature, these parameters are defined as follows:

• *Total quantum cost* is the number of 1-qutrit permutation gates required to realize the quantum ternary circuit.

- **Depth** is the number of timesteps required to realize the corresponding quantum circuit [49]. One or more quantum ternary gates that act on disjoint qutrit can be executed in each timestep in parallel.

- *The number of constant inputs* is the number of inputs to be kept constant at 0, 1, or 2 in order to synthesize a logic function.

- *The number of Garbage outputs* is the number of unused outputs to maintain the reversibility of the logic functions.

The paper is organized as follows: Sect. 2 presents ternary logic and ternary Galois Field, and quantum ternary gates, which are used in the following sections to design our proposed circuits. Section 3 presents the realization of our proposed quantum reversible ternary decoder, multiplexer, and demultiplexer circuits. In Sect. 4, the assessment of the proposed circuits is discussed, and finally, the conclusion is given in Sect. 5.

## 2 Preliminaries

The basic concepts of quantum ternary logic are presented in this section. We will also introduce ternary Galois Field 3 (GF3) and corresponding multiplication and addition operations in GF3. Moreover, this section includes quantum ternary permutation, Muthukrishnan-Stroud, and Controlled Feynman gates, which were used to construct our proposed designs in the next sections.

#### 2.1 Quantum ternary logic and qutrit

In quantum multiple-valued logic, quantum ternary logic is the most popular type. In comparison with binary logic, quantum ternary logic offers several advantages, including higher security [35, 36], stronger quantum information processing [37], higher density of stored information, reduced interconnection complexity and area [38], lower power consumption and improved fault tolerance [39]. Ternary quantum computation achieves higher error tolerance when compared to binary quantum computation [55]. In a quantum ternary system, the unit of information is called qutrit (quantum ternary digit). There are three basic states for a qutrit, namely  $|0\rangle$ ,  $|1\rangle$ , and  $|2\rangle$ . These basic states are called qutrit states and can be represented by  $3 \times 1$  vectors [25\_ENREF\_11]:

$$|0\rangle = \begin{bmatrix} 1\\0\\0 \end{bmatrix} \quad |1\rangle = \begin{bmatrix} 0\\1\\0 \end{bmatrix} \quad |2\rangle = \begin{bmatrix} 0\\0\\1 \end{bmatrix}$$

(5)

Qutrits can be represented by linear superpositions of basis states in a quantum ternary system. Superposition is the term for this technique, which can be defined with the following equation:

$$\psi = \alpha |0\rangle + \beta |1\rangle + \gamma |2\rangle \tag{6}$$

where  $\psi$  is the wave function and  $\alpha$ ,  $\beta$ , and  $\gamma$  are complex numbers. The quantum ternary system may be in each basis state with a specified probability. The probability measurement of the occurrences for state  $|0\rangle$  is equal to  $|\alpha|^2$ , for state  $|1\rangle$  is  $|\beta|^2$ , and for state  $|2\rangle$  is equal to  $|\gamma|^2$ . The sum of these probabilities is shown in the following:

$$|\alpha|^2 + |\beta|^2 + |\gamma|^2 = 1 \tag{7}$$

## 2.2 Ternary galois field

In this section, an introduction to the ternary Galois Field 3 (GF3) is provided. The GF3 algebraic structure is composed of three elements  $T = \{0, 1, 2\}$  and two primitive binary operations that are module 3. Table 1 and Table 2 show the operations of addition ( $\oplus$ ) and multiplication ( $\odot$ ), respectively [26, 40].

GF3 operations satisfy the following axioms. As can be seen, operations in GF3 are associative and commutative. Moreover, multiplication is distributive over addition.

**Axiom 1:**  $a \oplus (b \oplus c) = (a \oplus b) \oplus c$  (Associative law for addition).

**Axiom 2:**  $a \oplus b = b \oplus a$  (Commutative law for addition).

**Axiom 3:**  $a \oplus 0 = a$  (Identity element for addition).

**Axiom 4:**  $a \oplus (-a) = 0$  (Inverse element for addition).

**Axiom 5:**  $a \odot (b \odot c) = (a \odot b) \odot c$  (Associative law for multiplication).

**Axiom 6:**  $a \odot b = b \odot a$  (Commutative law for multiplication).

**Axiom 7:**  $a \odot l = a$  (Identity element for multiplication).

Axiom 8:  $a \odot a^{-1} = 1$  (Inverse element for multiplication).

**Axiom 9:**  $a \odot (b \oplus c) = (a \odot b) \oplus (a \odot c)$  (Distributive law).

| <b>Table 1</b> The truth table of GF 3addition operation [26, 29]                | $\oplus$ | 0 | 1 | 2 |

|----------------------------------------------------------------------------------|----------|---|---|---|

|                                                                                  | 0        | 0 | 1 | 2 |

|                                                                                  | 1        | 1 | 2 | 0 |

|                                                                                  | 2        | 2 | 0 | 1 |

| <b>Table 2</b> The truth table of GF 3         multiplication operation [26, 29] |          | 0 | 1 | 2 |

| multiplication operation [20, 27]                                                |          |   |   |   |

|                                                                                  | 0        | 0 | 0 | 0 |

|                                                                                  | 1        | 0 | 1 | 2 |

|                                                                                  | 2        | 0 | 2 | 1 |

#### 2.3 Ternary permutation gates

In ternary logic, there are 3! = 6 possible permutations of 0, 1, and 2. Accordingly, a ternary logic variable can be transformed in 6 ways using unitary transformations. The truth tables for these transforms can be seen in Table 3.

According to Table 3, the value of the variable *a* changes from *x* to *y* and *y* to *x* without changing the other values if transforms of the form Z(xy) (where  $x, y \in \{0, 1, 2\}$ ) and  $x \neq y$ , are applied on a variable *a*. The value of the variable *a* will become  $a \oplus x$  when the transforms of the form Z(+x) (where  $x \in \{0, 1, 2\}$ ) are applied on a variable *a*.

All transforms can also be represented by  $3 \times 3$  matrixes. Any of these matrixes can be presented by a 1-qutrit permutation gate [30, 41]. Figure 1 illustrates 1-qutrit permutative transforms.

In the Z (+ 0) transformation, each column shows 0, 1, and 2, respectively, and it is known as an elementary state. In Z (+ 1) transformation, the qutrit states are Z (+ 0) shifted by 1, in Z (+ 2) transformation, the qutrits in elementary state shift by 2; with Z (12) transformation, the qutrit states  $|1\rangle$  and  $|2\rangle$  in Z (+ 0) will be exchanged, Z (01) exchanges qutrit states  $|0\rangle$  and  $|1\rangle$  in the elementary state, and with Z (02)qutrit states  $|0\rangle$  and  $|2\rangle$  will be exchanged. These transformations can be presented as 1-qutrit permutation gates. In the literature, each of these gates has various names [41-44, 56], Z(+0) is called buffer and represents a quantum wire; Z(+2) is named C2 and dual-shift; Z(+1) is called C1 and single-shift; Z(12) is termed D and self-shift; Z(01) called E and self-single-shift, and Z(02) is called N inverse and self-dual-shift. Figure 2 shows the symbolic representation of 1-qutrit permutation gates. In this gate,

| Transform | Z(+ 0) | Z(+ 1) | Z(+ 2) | Z(12) | Z(01) | Z(02) |

|-----------|--------|--------|--------|-------|-------|-------|

| Input 012 | 012    | 120    | 201    | 021   | 102   | 210   |

Table 3 Ternary permutative unitary transforms [18]

| $Z(+0) = \begin{bmatrix} 1\\0\\0 \end{bmatrix}$ | 0<br>1<br>0 | $\begin{pmatrix} 0\\0\\1 \end{bmatrix}$     | $Z\left(+l\right) = \begin{bmatrix} 0\\1\\0 \end{bmatrix}$ | 0<br>0<br>1 | $\begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}$ | $Z(+2) = \begin{bmatrix} 0\\0\\1 \end{bmatrix}$ | 1<br>0<br>0 | $\begin{bmatrix} 0\\1\\0 \end{bmatrix}$     |

|-------------------------------------------------|-------------|---------------------------------------------|------------------------------------------------------------|-------------|---------------------------------------------|-------------------------------------------------|-------------|---------------------------------------------|

| $Z(12) = \begin{bmatrix} 1\\0\\0 \end{bmatrix}$ | 0<br>0<br>1 | $\begin{bmatrix} 0 \\ 1 \\ 0 \end{bmatrix}$ | $Z(01) = \begin{bmatrix} 0\\1\\0 \end{bmatrix}$            | 1<br>0<br>0 | $\begin{pmatrix} 0\\0\\1 \end{bmatrix}$     | $Z(02) = \begin{bmatrix} 0\\0\\1 \end{bmatrix}$ | 0<br>1<br>0 | $\begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}$ |

Fig. 1 1-qutrit permutative transforms [26, 30]

Fig. 2 Symbol of 1-qutrit permutation gates [25]

| Table 4 Ternary 1 | - quuit gales and in | en niverse gates [1 | 0]    |       |       |

|-------------------|----------------------|---------------------|-------|-------|-------|

| Gate              | Z(+ 1)               | Z(+ 2)              | Z(12) | Z(01) | Z(02) |

| Inverse gate      | Z(+ 2)               | Z(+ 1)              | Z(12) | Z(01) | Z(02) |

Table 4 Ternary 1- qutrit gates and their inverse gates [18]

the output *P* is equal to *Z* transform (where  $Z = \{+0, +1, +2, 01, 02, 12\}$ ) of input A. The quantum cost of these gates is 1.

As an example, for 1-qutrit permutation gates, when the transform is Z (+2) and the variable *a* is 1, we have:

$$Z (+2) = \begin{bmatrix} 0 & 1 & 0 \\ 0 & 0 & 1 \\ 1 & 0 & 0 \end{bmatrix} \qquad a = |1\rangle = \begin{bmatrix} 0 \\ 1 \\ 0 \end{bmatrix}$$

(8)

Application of a transform Z on a variable a is computed as the matrix multiplication of Z.a. The computation of Z(+2).a is as follows:

$$\begin{bmatrix} 0 & 1 & 0 \\ 0 & 0 & 1 \\ 1 & 0 & 0 \end{bmatrix} \cdot \begin{bmatrix} 0 \\ 1 \\ 0 \end{bmatrix} = \begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}$$

(9)

As can be seen in Table 3, when the input is 1, and the transform is Z (+2), the result is 0. It is worth mentioning that each of the 1-qutrit permutation gates has a unitary inverse gate which is utilized in order to restore the inputs [45, 46]. Inverse gates for each 1-qutrit permutation gate are illustrated in Table 4. As shown in this table, Z (01), Z (02), and Z (12) are self-inverse gates.

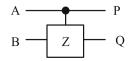

#### 2.4 Ternary muthukrishnan-stroud gates

Muthukrishnan and Stroud designed 2-qutrit quantum gates and demonstrated their ion-trap realizations [25]. Figure 3 shows the graphical symbol used for 2-qutrit Muthukrishnan-Stroud (M-S) gate. As shown, the inputs for this gate are A and B, and the outputs are P and Q where P equals A and Q equals Z transform (where  $Z = \{+1, +2, 01, 02, 12\}$ ) of B when A = 2, otherwise Q = B. This gate has a quantum cost of 1.

Fig. 3 Symbol of 2-qutrit Muthukrishnan-Stroud gate [25]

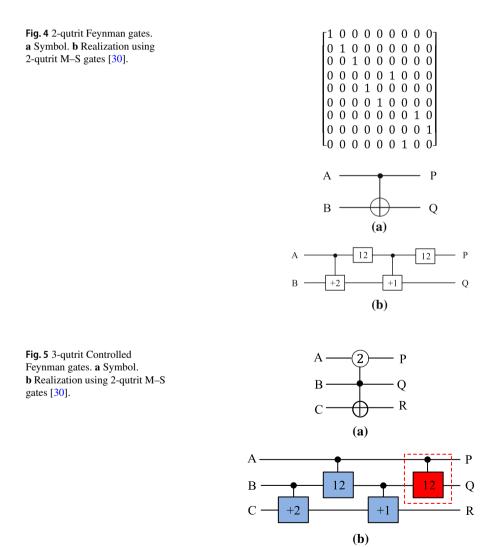

### 2.5 Ternary controlled feynman gate

Figure 4a shows the symbolic representation of the ternary Feynman gate. As shown, the inputs for this gate are A and B, and the outputs are P and Q where P equals A and Q equals  $A \oplus B$ . This gate can be realized using Muthukrishnan-Stroud gates and 1-qutrit permutation gates in Fig. 4b. According to the proofs stated in [47, 48] ternary Feynman gate evaluation matrix can be expressed as:

H.A Khan in [30] designed ternary Controlled Feynman gate and demonstrated their realization using 2-qutrit Muthukrishnan-Stroud gates. Figure 5a illustrates the symbolic representation of the ternary Controlled Feynman gate. As can be seen, the inputs for this gate are A, B, and C, and the outputs are P, Q, and R. P equals A, Q

equals *B*, and *R* equals  $B \oplus C$  when A = 2; otherwise, R = C. This gate can be realized using Muthukrishnan-Stroud gates and 1-qutrit permutation gates in Fig. 5b. Resulting in a quantum cost of 4 for this gate. It is possible to remove the fourth 2-qutrit M-S gate in the red box if input *B* is not needed at the output *Q*. The quantum cost is reduced to 3 in this way.

## 3 The proposed quantum ternary circuits

In this section, we first propose two quantum ternary decoders. The quantum ternary multiplexer and demultiplexer circuits are then presented. The following subsections describe these designs in detail.

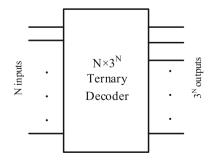

#### 3.1 The proposed quantum ternary decoder circuits

One of the important ternary combinational logic circuits is the ternary decoder which converts ternary information from the *N* inputs to  $3^N$  unique outputs. Figure 6 illustrates the block diagram of  $N \times 3^N$  ternary decoder circuit. Table 5 shows the truth table of  $2 \times 9$  ternary decoders with active-2 output. In this table, *A* and *B* are the input variables, whereas *D0*, *D1*, *D2*, *D3*, *D4*, *D5*, *D6*, *D7*, and *D8* are the output variables. For each combination of inputs, only one output line will be activated. Here, the circuit is active-2, i.e. if the output line is 2, then the line is ON; otherwise, it is OFF.

According to the above true table, only one of the outputs will be 2 for a given input combination. The outputs are equal to:

| D0 = A0B0 | D1 = A0B1 | D2 = A0B2 |

|-----------|-----------|-----------|

| D3 = A1B0 | D4 = A1B1 | D5 = A1B2 |

| D6 = A2B0 | D7 = A2B1 | D8 = A2B2 |

The outputs x in Table 5 can be either 0 or 1. In both cases, the output line will be inactive.

Here we present two approaches to constructing the proposed quantum ternary decoder.

**Fig. 6** Block diagram of  $N \times 3^N$  ternary multiplexer circuit

| Inputs (AB) | Outpu | ts |    |    |    |    |    |    |    |

|-------------|-------|----|----|----|----|----|----|----|----|

|             | D0    | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 |

| 00          | 2     | x  | х  | х  | х  | х  | x  | х  | x  |

| 01          | x     | 2  | х  | x  | х  | x  | х  | x  | х  |

| 02          | х     | х  | 2  | х  | х  | х  | х  | х  | х  |

| 10          | х     | х  | х  | 2  | х  | х  | х  | х  | х  |

| 11          | х     | х  | х  | х  | 2  | х  | х  | х  | х  |

| 12          | х     | х  | х  | х  | х  | 2  | х  | х  | х  |

| 20          | х     | х  | х  | х  | х  | х  | 2  | х  | х  |

| 21          | х     | x  | x  | х  | x  | х  | x  | 2  | х  |

| 22          | х     | х  | х  | х  | х  | х  | х  | х  | 2  |

**Table 5**  $2 \times 9$  ternary decoder truth table.

x: OFF, 2: ON.

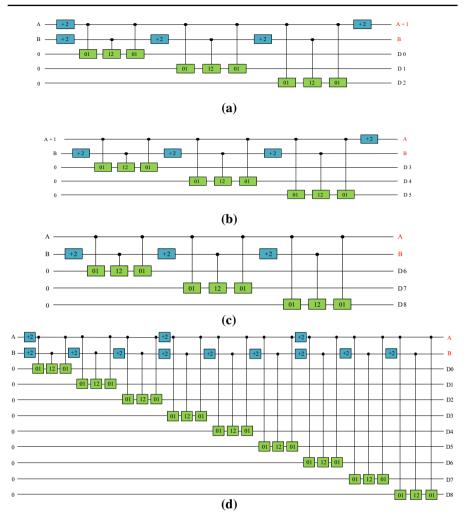

#### 3.1.1 The primary quantum ternary decoder design approach

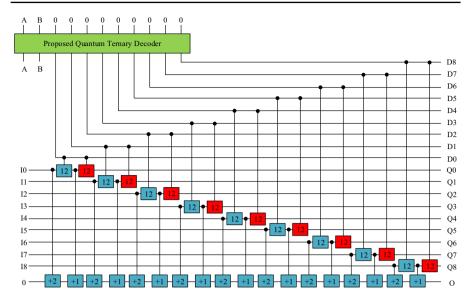

In the Primary Quantum Ternary Decoder Design Approach (*PQTDA*), only one of the outputs will be equal to 2 for a given input combination, and the remaining outputs will be equal to 0 (i.e., x = 0). For better comprehension, first, we show the quantum ternary decoder operation in three parts (Fig. 7a-c). Then show the complete design in Fig. 7d. The realization of the first part is shown in Fig. 7a, which consists of five 1-qutrit permutation gates and nine 2-qutrit Muthukrishnan–Stroud gates. In the first part, if inputs *A* and *B* are equal to 00, only output *D*0 will be equal to 2; however, when inputs *A* and *B* are 01, only output *D*1 is 2; whereas if *A* and *B* are 02 will result in output *D*2 to be 2.

The realization of the second part is shown in Fig. 7b using five 1-qutrit permutation gates and nine 2-qutrit Muthukrishnan–Stroud gates. In this part, if inputs A and B are equal to 10, only output D3 will be equal to 2; when inputs A and B are 11, output D4 is 2; and if A and B are 12, output D5 will be 2.

The realization of the last part is shown in Fig. 7c. In this part, if the inputs A and B are equal to 20, only the output D6 will be equal to 2; when inputs A and B are 21, output D7 will be 2; and finally, if A and B are 22, output D8 will be 2. The realization of the proposed quantum ternary decoder is shown in Fig. 7d. As can be seen, twelve 1-qutrit permutation gates and twenty-seven 2-qutrit Muthukrishnan–Stroud gates were used in the proposed decoder. This circuit has a quantum cost of 39. The outputs of this circuit for different input combinations are illustrated in Table 6. The depth of the proposed quantum ternary decoder circuit in Fig. 7d is 30.

#### 3.1.2 Optimized quantum ternary decoder design approach

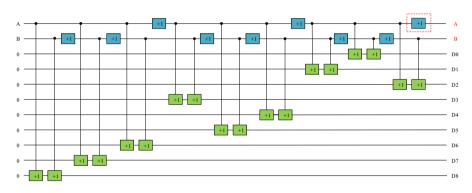

In the Optimized Quantum Ternary Decoder Design Approach (*OQTDA*), we present a lower quantum cost ternary decoder. In this optimized realization, all unselected

**Fig. 7** The proposed *PQTDA*. **a** The first part. **b** The second part. **c** The third part. **d** Complete realization of *PQTDA* using 2-qutrit M–S and 1-qutrit permutation gates

outputs are allowed to take on the value 1 or 0 while only the selected output to be equal to 2. To design this circuit, we have used 1-qutrit permutation gates and 2-qutrit Muthukrishnan–Stroud. The proposed circuit is realized in Fig. 8. As shown, nine 1-qutrit permutation gates and eighteen 2-qutrit Muthukrishnan–Stroud gates are used. The quantum cost of this circuit is 27, resulting in a great improvement with respect to overall implementation cost and circuit depth as compared to *PQTDA*. The outputs of this circuit are shown in Table 7. The depth of the proposed quantum ternary decoder circuit in Fig. 8 is 18. It is to be noted that in *OQTDA*, at the first line, the output is restored to input A. If it is not essential to restore this input at the output, we can remove the last + 1 gate, which is marked with a red-colored dashed line in Fig. 8. As

## Table 6 PQTDA truth table

| Inputs (AB) | Outpu | ts |    |    |    |    |    |    |    |

|-------------|-------|----|----|----|----|----|----|----|----|

|             | D0    | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 |

| 00          | 2     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 01          | 0     | 2  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 02          | 0     | 0  | 2  | 0  | 0  | 0  | 0  | 0  | 0  |

| 10          | 0     | 0  | 0  | 2  | 0  | 0  | 0  | 0  | 0  |

| 11          | 0     | 0  | 0  | 0  | 2  | 0  | 0  | 0  | 0  |

| 12          | 0     | 0  | 0  | 0  | 0  | 2  | 0  | 0  | 0  |

| 20          | 0     | 0  | 0  | 0  | 0  | 0  | 2  | 0  | 0  |

| 21          | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 2  | 0  |

| 22          | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 2  |

0: OFF, 2: ON

Table 7 OQTDA truth table

| Inputs (AB) | Outpu | ts |    |    |    |    |    |    |    |

|-------------|-------|----|----|----|----|----|----|----|----|

|             | D0    | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 |

| 00          | 2     | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 0  |

| 01          | 1     | 2  | 1  | 0  | 1  | 0  | 0  | 1  | 0  |

| 02          | 1     | 1  | 2  | 0  | 0  | 1  | 0  | 0  | 1  |

| 10          | 1     | 0  | 0  | 2  | 1  | 1  | 1  | 0  | 0  |

| 11          | 0     | 1  | 0  | 1  | 2  | 1  | 0  | 1  | 0  |

| 12          | 0     | 0  | 1  | 1  | 1  | 2  | 0  | 0  | 1  |

| 20          | 1     | 0  | 0  | 1  | 0  | 0  | 2  | 1  | 1  |

| 21          | 0     | 1  | 0  | 0  | 1  | 0  | 1  | 2  | 1  |

| 22          | 0     | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 2  |

0, 1: OFF, 2: ON

a result, the quantum cost is reduced to 26, and the output on the first line will become A + 2.

## 3.2 The proposed quantum ternary multiplexer circuit

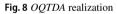

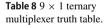

A multiplexer circuit has one output, multiple inputs, and selectors. Selectors specify which inputs are gated to the output. A ternary multiplexer takes *N* ternary numbers as selectors and  $3^N$  ternary numbers as input and gives output as a number. The block diagram of  $3^N \times 1$  ternary multiplexer circuit is illustrated in Fig. 9. Table 8 shows the truth table of  $9 \times 1$  ternary multiplexer, where *A* and *B* are selectors, and *I0*, *I1*, *I2*, *I3*, *I4*, *I5*, *I6*, *I7*, and *I8* are the inputs, and the output is depicted as *O*. For a given selector combination, only the selected input will be gated to the output.

According to Table 8, the output is equal to:

O = (A0B0) I0 + (A0B1) I1 + (A0B2) I2 + (A1B0) I3 + (A1B1) I4 + (A1B2) I5 + (A2B0) I6 + (A2B1) I7 + (A2B2) I8.

To construct a ternary multiplexer circuit, we use the proposed quantum ternary decoder and ternary Controlled Feynman gates. The realization of the proposed multiplexer is shown in Fig. 10. In this circuit, input restoration is necessary, where *PQTDA*, nine ternary controlled Feynman, and sixty-three 2-qutrit Muthukrishnan–Stroud gates are used. In this implementation, the outputs preserve their corresponding inputs by

N selectors

| Selectors (AB) | Output (O) |

|----------------|------------|

| 00             | ΙΟ         |

| 01             | I1         |

| 02             | I2         |

| 10             | 13         |

| 11             | I4         |

| 12             | 15         |

| 20             | I6         |

| 21             | I7         |

| 22             | 18         |

outputs

Fig. 10 Realization of the proposed quantum ternary multiplexer circuit

utilizing nine Muthukrishnan–Stroud gates shown in red in the figure, resulting in a total quantum cost of 75. Cost can be further decreased to 53 if input restoration is not necessary and can be accomplished using *OQTDA* and removing the 1-qutrit permutation gates shown in red from Fig. 10.

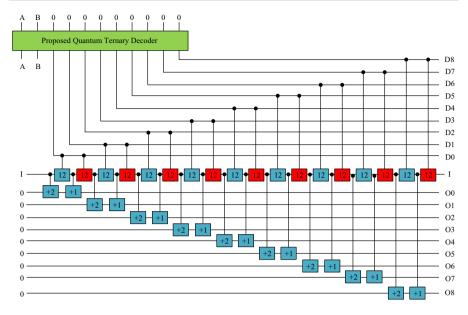

# 3.3 The proposed quantum ternary demultiplexer circuit

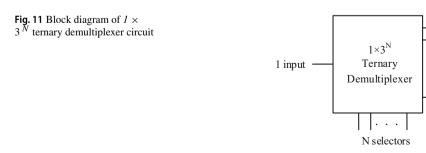

A demultiplexer circuit has one input, multiple outputs, and selectors. The selector specifies how the input is switched to the specified output. A ternary demultiplexer takes N ternary numbers as selectors and one ternary number as input and gives  $3^N$  numbers as outputs. The block diagram of  $1 \times 3^N$  ternary demultiplexer is shown in Fig. 11, whereas Table 9 shows the truth table of  $1 \times 9$  ternary demultiplexer. The input is specified as I, selectors are A and B, and outputs as O. Only one of the outputs will be equal to I for a given selectors combination, and the remaining ones will be O.

| Selectors (AB) | Outputs |    |    |    |    |    |    |    |    |

|----------------|---------|----|----|----|----|----|----|----|----|

|                | 00      | 01 | 02 | O3 | O4 | 05 | O6 | 07 | 08 |

| 00             | Ι       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 01             | 0       | Ι  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 02             | 0       | 0  | Ι  | 0  | 0  | 0  | 0  | 0  | 0  |

| 10             | 0       | 0  | 0  | Ι  | 0  | 0  | 0  | 0  | 0  |

| 11             | 0       | 0  | 0  | 0  | Ι  | 0  | 0  | 0  | 0  |

| 12             | 0       | 0  | 0  | 0  | 0  | Ι  | 0  | 0  | 0  |

| 20             | 0       | 0  | 0  | 0  | 0  | 0  | Ι  | 0  | 0  |

| 21             | 0       | 0  | 0  | 0  | 0  | 0  | 0  | Ι  | 0  |

| 22             | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Ι  |

**Table 9**  $1 \times 9$  ternary demultiplexer truth table.

According to Table 9, The outputs are equal to:

| O0 = A0B0I | O1 = A0B1I | O2 = A0B2I |

|------------|------------|------------|

| O3 = A1B0I | O4 = A1B1I | O5 = A1B2I |

| O6 = A2B0I | O7 = A2B1I | O8 = A2B2I |

The proposed decoder and ternary-controlled Feynman gates are used to construct the ternary demultiplexer circuit. The proposed quantum ternary demultiplexer is realized in Fig. 12. In this circuit, input restoration is necessary, and the proposed *PQTDA* and nine ternary controlled-Feynman gates are utilized. By using the red-colored Muthukrishnan–Stroud gates, inputs can be restored, leading to a total quantum cost of 75. However, if input restoration is not necessary, then *OQTDA* design can be used, along with removing red-colored gates, decreasing the quantum cost to 53.

## 4 Result assessment

The proposed quantum ternary decoders, multiplexer, and demultiplexer are analyzed with respect to their quantum cost, depth, number of garbage outputs, and constant inputs. These are the most important metrics to evaluate the efficiency of any quantum circuits.

Table 10 compares our proposed quantum ternary decoder circuit with its counterpart in [31]. As can be seen, the proposed decoder (*OQTDA*) has less quantum cost, depth, garbage outputs, and constant inputs than the design in [31], eliminating 27 M-S gates and four permutation gates and reducing by one both constant input and garbage output.

According to Table 10, the proposed multiplexer improves quantum cost, depth, garbage outputs, and constant inputs when compared with the similar circuit suggested

Fig. 12 Realization of the proposed ternary demultiplexer circuit

in [30]. In particular, the improvement in quantum cost, depth, garbage outputs, and constant inputs are 48%, 41%, 4%, and 9%, respectively.

The comparison in Table 10 clearly demonstrates the proposed design of the demultiplexer leads to improvements in terms of quantum cost (48%), depth (41%), garbage outputs (7%), and constant inputs (5%) as compared to its counterpart in [30].

It should be noted that although all the proposed designs are more efficient when compared with the circuits suggested in [30, 31], the comparison has been done using the best-proposed designs, which do not restore inputs.

# **5** Conclusion

Quantum ternary circuits are the new generation of quantum circuits, and they have advantages over their binary counterparts. Many quantum ternary circuits and optimization approaches to construct different computational units of quantum computers and other complicated systems have been investigated in the literature. This paper proposes two new realizations of quantum ternary decoder by using 1-qutrit permutation gates and 2-qutrit Muthukrishnan–Stroud gates. We have also presented quantum ternary multiplexer and demultiplexer based on the realization of the decoder circuit. The proposed circuits in this work reduce quantum cost, depth, the number of garbage outputs, and constant inputs. Since the lower values of these figures of merit lead to more efficient quantum ternary circuit designs compared to the existing counterparts, our proposed realizations are more efficient. In addition, the proposed designs in this

|                                    | Decoder Designs | igns              |                                          | Multiplexer Designs | lesigns           |                                          | Demultiplexer Designs | Designs           |                           |

|------------------------------------|-----------------|-------------------|------------------------------------------|---------------------|-------------------|------------------------------------------|-----------------------|-------------------|---------------------------|

|                                    | oQTDA           | Design in<br>[31] | Design in Improvement<br>[31] percentage | Proposed<br>design  | Design in<br>[30] | Design in Improvement<br>[30] percentage | Proposed<br>design    | Design in<br>[30] | Improvement<br>percentage |

| Quantum<br>Cost                    | 26              | 57                | 54%                                      | 53                  | 102               | 48%                                      | 53                    | 102               | 48%                       |

| Depth                              | 18              | 54                | 66%                                      | 44                  | 75                | 41%                                      | 44                    | 75                | 41%                       |

| Constant<br>Input                  | 6               | 10                | 10%                                      | 10                  | 11                | 9%6                                      | 18                    | 19                | 5%                        |

| Garbage<br>Output                  | 7               | ε                 | 33%                                      | 20                  | 21                | 4 <i>%</i>                               | 12                    | 13                | 7%                        |

| Input<br>restoration<br>capability | No              | Yes               | I                                        | No                  | Yes               | 1                                        | No                    | Yes               | 1                         |

Table 10 Evaluation of quantum ternary decoder, multiplexer, and demultiplexer circuits

study can be utilized to design various components for ternary quantum computers and other intricate computational systems.

## 6 Data availability statement

Data sharing is not applicable to this article as no datasets were generated or analyzed during the current study.

Acknowledgements This research has been supported by the Academy of Finland (Project 349945).

Author contributions All authors contributed equally to the paper. All authors read and approved the final manuscript.

**Funding** Open Access funding provided by University of Jyväskylä (JYU). Open Access funding was provided by the University of Jyväskylä (JYU).

## Declarations

Conflict of interest The authors declare no conflict of interest.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

## References

- Haghparast, M., Mohammadi, M., Navi, K., Eshghi, M.: Optimized reversible multiplier circuit. J. Circuits, Syst. Comput. 18(02), 311–323 (2009)

- Alexandrescu, D., Altun, M., Anghel, L., Bernasconi, A., Ciriani, V., Frontini, L., Tahoori, M.: Logic synthesis and testing techniques for switching nano-crossbar arrays. Microprocess. Microsyst. 54, 14–25 (2017)

- Landauer, R.: Irreversibility and heat generation in the computing process. IBM J. Res. Dev. 5(3), 183–191 (1961)

- Seyedi, S., Jafari Navimipour, N.: Designing a multi-layer full-adder using a new three-input majority gate based on quantum computing. Concurrency and Comput.: Practice and Exp. 34(4), e6653 (2022)

- Klimov, A.B., Guzman, R., Retamal, J.C., Saavedra, C.: Qutrit quantum computer with trapped ions. Phys. Rev. A 67(6), 062313 (2003)

- Mc Hugh, D., Twamley, J.: Trapped-ion qutrit spin molecule quantum computer. New J. Phys. 7(1), 174 (2005)

- Muthukrishnan, A., Stroud, C.R., Jr.: Multivalued logic gates for quantum computation. Phys. Rev. A 62(5), 052309 (2000)

- Das, R., Mitra, A., Kumar, S.V., Kumar, A.: Quantum information processing by NMR: preparation of pseudopure states and implementation of unitary operations in a single-qutrit system. Int. J. Quantum Inform. 1(03), 387–394 (2003)

- Zhang, P., Wu, H., Chen, J., Khan, S.A., Krogstrup, P., Pekker, D., Frolov, S.M.: Signatures of andreev blockade in a double quantum dot coupled to a superconductor. Phys. Rev. Lett. 128(4), 046801 (2022)

- Chi, Y., Huang, J., Zhang, Z., Mao, J., Zhou, Z., Chen, X., Wang, J.: A programmable qudit-based quantum processor. Nat. Commun. 13(1), 1–10 (2022)

- 11. Bennett, C.H.: Logical reversibility of computation. IBM J. Res. Dev. 17(6), 525-532 (1973)

- 12. Nielson, M. A., & Chuang, I. L. (2000). Quantum computation and quantum information.

- Haghparast, M., Bolhassani, A.: Optimized parity preserving quantum reversible full adder/subtractor. Int. J. Quantum Inform. 14(03), 1650019 (2016)

- Haghparast, M., Mohammadi, M.: Novel quantum compressor designs using new genetic algorithmbased simulator, analyzer, and synthesizer software in nanotechnology. Int. J. Quantum Inform. 8(07), 1219–1231 (2010)

- Haghparast, M., Navi, K.: Novel reversible fault tolerant error coding and detection circuits. Int. J. Quantum Inform. 9(02), 723–738 (2011)

- Ehsanpour, M., Cimato, S., Ciriani, V., & Damiani, E. (2017, August). Exploiting quantum gates in secure computation. In 2017 Euromicro Conference on Digital System Design (DSD) (pp. 291–294). IEEE.

- Garipelly, R., Kiran, P.M., Kumar, A.S.: A review on reversible logic gates and their implementation. Int. J. Emerg. Technol. Adv. Eng. 3(3), 417–423 (2013)

- Khan, M.H., Perkowski, M.A.: Quantum ternary parallel adder/subtractor with partially-look-ahead carry. J. Syst. Architect. 53(7), 453–464 (2007)

- Khan, M. H. (2010, September). GFSOP-based ternary quantum logic synthesis. In Optics and Photonics for Information Processing IV (Vol. 7797, pp. 110–124). SPIE.

- Haghparast, M., Wille, R., Monfared, A.T.: Towards quantum reversible ternary coded decimal adder. Quantum Inf. Process. 16(11), 1–25 (2017)

- Asadi, M.A., Mosleh, M., Haghparast, M.: Towards designing quantum reversible ternary multipliers. Quantum Inf. Process. 20(7), 1–27 (2021)

- Mercy Nesa Rani, P., & Thangkhiew, P. L. (2022). An Overview of Different Approaches for Ternary Reversible Logic Circuits Synthesis Using Ternary Reversible Gates with Special Reference to Virtual Reality. Advances in Augmented Reality and Virtual Reality, 73–90.

- 23. Panahi, M.M., Hashemipour, O., Navi, K.: A novel design of a ternary coded decimal adder/subtractor using reversible ternary gates. Integration **62**, 353–361 (2018)

- Panahi, M.M., Hashemipour, O., Navi, K.: A novel design of a multiplier using reversible ternary gates. IETE J. Res. 67(6), 744–753 (2021)

- Monfared, A.T., Haghparast, M.: Quantum ternary multiplication gate (QTMG): toward quantum ternary multiplier and a new realization for ternary toffoli gate. J. Circuits, Syst. Comput. 29(05), 2050071 (2020)

- Monfared, A.T., Haghparast, M.: Design of new quantum/reversible ternary subtractor circuits. J. Circuits, Syst. Comput. 25(02), 1650014 (2016)

- Asadi, M.A., Mosleh, M., Haghparast, M.: Toward novel designs of reversible ternary 6: 2 Compressor using efficient reversible ternary full-adders. J. Supercomput. 77(5), 5176–5197 (2021)

- Monfared, A.T., Haghparast, M.: Designing new ternary reversible subtractor circuits. Microprocess. Microsyst. 53, 51–56 (2017)

- Taheri Monfared, A., Haghparast, M., Datta, K.: Quaternary quantum/reversible half-adder, full-adder, parallel adder and parallel adder/subtractor circuits. Int. J. Theor. Phys. 58(7), 2184–2199 (2019)

- Khan M. H.: Design of Reversible/Quantum Ternary Multiplexer and Demultiplexer. Engineering letters, 13(3). (2006)

- Khan, M. H., & Perkowski, M.: Quantum realization of ternary encoder and decoder. In Proc. 7th Int. Symp. Representations and Methodology of Future Computing Technologies (RM2005), Tokyo, Japan. (2005)

- Paler, A., Basmadjian, R.: Energy cost of quantum circuit optimisation: predicting that optimising shor's algorithm circuit uses 1 GWh. ACM Trans. Quantum Comput. 3(1), 1–14 (2022)

- Barenco, A., Bennett, C.H., Cleve, R., DiVincenzo, D.P., Margolus, N., Shor, P., Weinfurter, H.: Elementary gates for quantum computation. Phys. Rev. A 52(5), 3457 (1995)

- Mohammadi, M., Eshghi, M.: On figures of merit in reversible and quantum logic designs. Quantum Inf. Process. 8(4), 297–318 (2009)

- Bechmann-Pasquinucci, H., Peres, A.: Quantum cryptography with 3-state systems. Phys. Rev. Lett. 85(15), 3313 (2000)

- Bourennane, M., Karlsson, A., Björk, G.: Quantum key distribution using multilevel encoding. Phys. Rev. A 64(1), 012306 (2001)

- Greentree, A.D., Schirmer, S.G., Green, F., Hollenberg, L.C., Hamilton, A.R., Clark, R.G.: Maximizing the Hilbert space for a finite number of distinguishable quantum states. Phys. Rev. Lett. 92(9), 097901 (2004)

- Bundalo, D., Bundalo, Z., Đorđević, B.: Design of quaternary logic systems and circuits. Facta universitatis-series: Electron. Energ. 18(1), 45–56 (2005)

- Miller, D.M., Thornton, M.A.: Multiple valued logic: concepts and representations. Synthesis Lectures on Digital Circuits and Syst. 2(1), 1–127 (2007)

- Khan, M. H., Perkowski, M. A., & Kerntopf, P. (2003, May). Multi-output Galois field sum of products synthesis with new quantum cascades. In 33rd International Symposium on Multiple-Valued Logic, 2003. Proceedings. (pp. 146–153). IEEE.

- Miller, D.M., Maslov, D., Dueck, G.W.: Synthesis of quantum multiple-valued circuits. J. Multiple Valued Logic and Soft Comput. 12(5/6), 431 (2006)

- De Vos, A., Raa, B., Storme, L.: Generating the group of reversible logic gates. J. Phys. A: Math. Gen. 35(33), 7063 (2002)

- Miller, D. M., Dueck, G. W., & Maslov, D.: A synthesis method for MVL reversible logic [multiple value logic]. In Proceedings. 34th international symposium on multiple-valued logic (pp. 74–80). IEEE. (2004)

- Dubrova, E.V., Muzio, J.C.: Generalized Reed-Muller canonical form for a multiple-valued algebra. Multiple-Valued Logic, An Int. J. 1, 65–84 (1996)

- Mohammadi, M., Niknafs, A., Eshghi, M.: Controlled gates for multi-level quantum computation. Quantum Inf. Process. 10(2), 241–256 (2011)

- Mohammadi, M.: Radix-independent, efficient arrays for multi-level n-qudit quantum and reversible computation. Quantum Inf. Process. 14(8), 2819–2832 (2015)

- Al-Rabadi, A., Casperson, L., Perkowski, M., Song, X.: Multiple-valued quantum logic. Quantum 10(2), 1 (2002)

- Mondal, B., Sarkar, P., Saha, P. K., & Chakraborty, S. (2013, May). Synthesis of balanced ternary reversible logic circuit. In 2013 IEEE 43rd International Symposium on Multiple-Valued Logic (pp. 334–339). IEEE.

- Pham, P., Svore, K.M.: A 2D nearest-neighbor quantum architecture for factoring in polylogarithmic depth. Quantum Inf. Comput. 13(11–12), 937–962 (2013)

- González-Cuadra, D., Zache, T. V., Carrasco, J., Kraus, B., & Zoller, P. (2022). Hardware efficient quantum simulation of non-abelian gauge theories with qudits on Rydberg platforms. arXiv preprint arXiv:2203.15541.

- Yeh, L., & van de Wetering, J. (2022). Constructing all qutrit controlled Clifford+ T gates in Clifford+ T. arXiv preprint arXiv:2204.00552.

- Prakash, S., Kalra, A.R., Jain, A.: A normal form for single-qudit Clifford+T operators. Quantum Inf Process 20, 341 (2021). https://doi.org/10.1007/s11128-021-03280-0

- Jahangir, M.Z., Mounika, J.: Design and simulation of an innovative CMOS ternary 3 to 1 multiplexer and the design of ternary half adder using ternary 3 to 1 multiplexer. Microelectron. J. 90, 82–87 (2019)

- Khan, M. H.: Design of Reversible/Quantum Ternary Comparator Circuits. Engineering Letters, 16(2). (2008)

- Knill, E.: Fault-tolerant postselected quantum computation: Schemes. arXiv preprint quantph/0402171. (2004)

- Khandelwal, A., & Chandra, M. G.: Quantum Image Representation Methods Using Qutrits. arXiv preprint arXiv:2207.09096. (2022)

- Ilyas, M., Cui, S., & Perkowski, M.: Ternary Logic Design in Topological Quantum Computing. arXiv preprint arXiv:2204.01000. (2022)

- Zheng, R.H., Ning, W., Yang, Z.B., Xia, Y., Zheng, S.B.: Demonstration of dynamical control of three-level open systems with a superconducting qutrit. New J. Phys. 24(6), 063031 (2022)

- Hanks, M., & Kim, M. S. (2022). Fault-tolerance in qudit circuit design. arXiv preprint arXiv:2202. 06831.

- P. Gokhale, J. M. Baker, C. Duckering, N. C. Brown, K. R. Brown, and F. T. Chong, in Proceedings of the 46th International Symposium on Computer Architecture (ACM, Phoenix Arizona, 2019) pp. 554–566.

- Gustafson, E. (2022). Noise Improvements in Quantum Simulations of sQED using Qutrits. arXiv preprint arXiv:2201.04546.

Majumdar, R., Basu, S., Ghosh, S., Sur-Kolay, S.: Quantum error-correcting code for ternary logic. Phys. Rev. A 97(5), 052302 (2018)

**Publisher's Note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.