## Università degli Studi di Milano facoltà di scienze matematiche, fisiche e naturali

## Dottorato di Ricerca in Informatica XXII ciclo

## Threats on Real, Emulated and Virtualized Intel x86 Machine Code Execution

Tesi di Giampaolo Fresi Roglia

Relatore Prof. Danilo Bruschi Coordinatore del Dottorato Prof. Ernesto Damiani

Anno Accademico 2009/2010

### **Abstract**

The Internet is very popular nowadays, it is used by a continuously growing number of users to transfer confidential data representing a big attractive to cybercriminals. Criminals whose interest is to spread malicious software through different threat vectors aiming to steal those confidential data and sell it in the underground market. Cybercriminals have all the interest in not being detected while perpetrating their intentions. Impeding such threats to spread has become of valuable importance. This goal can be achieved working on the threat vectors cybercriminals use or directly on the threat once identified.

Among threat vectors we can cite application software vulnerabilities which can be abused by malware and malicious users to gain access to systems and confidential data. To be able to impede exploitation of such vulnerabilities, security specialists need to be aware of attack techniques used by malware and malicious users for to be able to design and implement effective protection techniques.

For identifying threats, it is of vital importance to use effective analysis tools which expose no weaknesses to malware authors giving them the chance to evade detection.

This dissertation presents two approaches for testing CPU emulators and system virtual machines which represent a fundamental component of dynamic malware analysis. These testing methodologies can be used to identify behavioural differences between real and emulated hardware. Differences exploitable by malware authors to detect emulation and hide their malicious behaviour.

This dissertation also presents a new exploitation technique against memory error vulnerabilities able to circumvent widely adopted protection strategies like  $W \oplus X$  and ASLR and the related countermeasure to impede exploitation.

## **Contents**

| I | Intr | oduction                                                    | V  |

|---|------|-------------------------------------------------------------|----|

|   | 1.1  | Summary of the contributions                                | Х  |

|   | 1.2  | Organisation of the dissertation                            | X  |

| 2 | Bac  | kground and Related work                                    | 1  |

|   | 2.1  | Overview of Intel x86 ISA                                   | 1  |

|   |      | 2.1.1 Challenges on x86 emulation                           | 2  |

|   | 2.2  | Software Testing                                            | 3  |

|   | 2.3  | Emulators in malware analysis                               | 4  |

|   | 2.4  | Buffer overflow                                             | 4  |

|   |      | 2.4.1 Notes on x86 unwanted code                            | 8  |

| 3 | Emi  | uFuzzer: a testing methodology for CPU emulators            | g  |

|   | 3.1  | Introduction                                                | Ć  |

|   | 3.2  | CPU Emulators                                               | 11 |

|   |      | 3.2.1 Faithful CPU Emulation                                | 11 |

|   |      | 3.2.2 Fuzzing CPU Emulators                                 | 13 |

|   | 3.3  | EmuFuzzer                                                   | 14 |

|   |      | 3.3.1 Test-case Generation                                  | 15 |

|   |      | 3.3.2 Test-case Execution                                   | 21 |

|   | 3.4  | Evaluation                                                  | 25 |

|   |      | 3.4.1 Experimental Setup                                    | 26 |

|   |      | 3.4.2 Evaluation of Test-case Generation                    | 26 |

|   |      | 3.4.3 Testing of IA-32 Emulators                            | 27 |

|   | 3.5  | Discussion                                                  | 29 |

| 4 | KEr  | nuFuzzer: a methodology for testing System Virtual Machines | 31 |

| - | 4.1  | Introduction                                                | 31 |

|   | 4.2  | Overview                                                    | 32 |

|   | 1.2  | 4.2.1 Virtualisation                                        | 33 |

|   |      | 4.2.2 Transparency of Virtual Machines                      | 34 |

|   |      | 4.2.3 Testing Transparency of Virtual Machines              | 34 |

|   |      |                                                             | _  |

| 4.3   | KEmuFuzzer                                    | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 4.3.1 Architecture and Methodology            | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 4.3.2 Test-cases                              | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 4.3.3 Kernel                                  | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 4.3.4 CPU Emulators and Virtualizers          | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 4.3.5 Oracle                                  | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.4   | Evaluation                                    | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 4.4.1 Experimental Setup                      | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 4.4.2 Test-cases                              | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 4.4.3 Experimental Results                    | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.5   | Discussion                                    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Dat   | ing to various dilities                       | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| _     |                                               | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.3   |                                               | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                                               | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| _ ,   |                                               | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.4   |                                               | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 0                                             | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.5   |                                               | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                                               | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                                               | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.6   | Discussion                                    | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Con   | clusions and future work                      | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| hling | ranhv                                         | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 4.4 4.5 <b>Ret</b> 5.1 5.2 5.3 5.4 <b>Con</b> | 4.3.1 Architecture and Methodology 4.3.2 Test-cases 4.3.3 Kernel 4.3.4 CPU Emulators and Virtualizers 4.3.5 Oracle 4.4 Evaluation 4.4.1 Experimental Setup 4.4.2 Test-cases 4.4.3 Experimental Results 4.5 Discussion  Returning to randomised lib(c) 5.1 Introduction 5.2 Background 5.3 Attack 5.3.1 Overview of the attack 5.3.2 Details of the attack 5.4 Attack mitigation 5.4.1 Preventing unsafe accesses to GOT 5.5 Evaluation 5.5.1 Evaluation of the attack 5.5.2 Evaluation of the proposed defence |

### 1 Introduction

Operating systems and application software become larger and more complex with every release. New features require the addition of new code, which typically contains new bugs. Bugs can be exploited by malicious users and malicious software to gain unauthorised access to systems and sensitive information. New vulnerabilities are discovered on a daily basis on a wide variety of application software. Malicious activities perpetrated through the Internet are becoming quickly a huge security problem, ranging between large-scale social engineering attacks and exploiting critical vulnerabilities. Attack techniques are becoming more sophisticated, malicious software authors are developing an arsenal of offensive techniques ranging from the use of polymorphism, metamorphism and cryptographically strong algorithms to render the task of identifying the threats they pose much more difficult. The goal of malicious activities is turning from disruption of services to the achievement of financial gain.

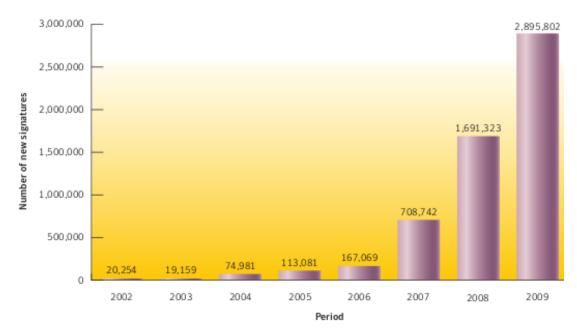

Figure 1.1 reports malicious code threats detected in 2009 (2,895,802) by Symantec, accounting for over 50% of the total amount of malicious code threats detected over time (approximately 5,700,000). This ever growing number of malicious code threats largely justifies the effort done by researchers for trying to defeat or at least mitigate their diffusion. The methods used by malicious software to spread are known with the name *Threat vectors*. One of the most used and effective threat vector is represented by remotely exploitable vulnerabilities. Malicious code employing such threat vector, according to Symantec account for 24% of the total. Even if remotely exploitable vulnerabilities is not the most used threat vector, it remains one of the most effective for the malware to spread rapidly and infect the maximum number of hosts possible. A notable example of malware using such threat vector is represented by the infamous *Conficker* worm, which, according to PandaLabs was able to infect almost 6% over a sample of 2 million computer analysed in 2008.

The vast majority of reported threats target the so called *Wintel* platform. The reason behind the choice by malware authors resides on the large-scale adoption of such "architecture" by the world-wide market. The Wintel platform represents a software *monocolture*. The large-scale adoption of this platform offers a large attack surface for malicious software to spread, i.e. exploiting a single vulnerability can result in compromising and taking control of a huge number of

**Figure 1.1:** New malicious code signatures

systems.

The fight against such threats can be done preventing vulnerabilities to be exploited or identifying threats after they already started to spread in the Internet. Prevention can be achieved by users, applying security patches once vulnerabilities are discovered or using anti-virus software and by security specialists, implementing protection techniques able to impede exploitation of vulnerable software.

From the malicious software analyst's point of view, it is of vital importance to recognise as soon as possible such threats as soon as they start to spread for to be able to develop quickly defence strategies against them. For this purpose techniques like static and dynamic binary analysis are employed. With these techniques, the malware analysts aim to recognise malicious behaviours in suspicious programs for providing signatures to intrusion prevention systems and anti-viruses. Unfortunately, malicious software authors are aware of such techniques used against their programs and they develop strategies to evade detection. Static analysis can be easily fooled with techniques like polymorphism and more generally by obfuscating the produced programs. Dynamic analysis by the way has its own limitations: it consists basically of executing the suspicious binary itself and observe its behaviour. For dynamic analysis to guarantee effectiveness, it must guarantee complete code coverage. This implies the observation of every possible execution path of the binary being analysed, objective which can be

reduced to the *halting problem* hence impossible to achieve in its full generality. Even with its limits, dynamic analysis is actually employed for run-time detection of malicious behaviours. Analysis of suspicious software is done in isolated environments (sandboxes) to prevent the potential malware to damage the analysis environment. For this purpose malware analysts employ software like system emulators for safely analyse such threats.

Lack of transparency of an emulator w.r.t. the emulated hardware can lead to evasion techniques against dynamic behavioural analysis of malware. If the malicious software were able to detect the presence of an emulator can react by not exposing it's malicious behaviour and stay potentially undetected and free to cause harm for a long time. The in-depth study of Intel x86 ISA (Instruction Set Architecture) gave us the chance of identifying some possible pitfalls which could render the task of correctly implementing an emulator very challenging. The machine-level x86 instruction space is redundant w.r.t. the assembly representation, i.e. an assembly representation can lead to differently encoded but semantically equivalent instructions. Redundancy can be a problem if unlikely used encodings point to the execution of buggy code in the emulator. Typical application software hardly covers the entire machine-level instruction space, so bugs can stay undetected for a long time in absence of the application of specific testing methodologies. Moreover, Intel manuals are written with the application software developer's needs in mind. They do not provide all the details needed for a completely correct implementation of an emulator, hence some side effects exposed by the execution of lots of instructions are left undocumented. manuals state those effects are to be considered "undefined". While this could be sufficient for application software to run correctly, implementing emulators based on those "specifications" may result in behavioural differences from the real hardware they are supposed to emulate.

This dissertation provides two specific testing methodologies for spotting differences (not just bugs) between the emulation software and the hardware it wishes to emulate. Information that could be used to harden an emulator to the point it satisfies the requirements for undetectability identified by Dinaburg *et al.* [15].

This dissertation also aims to show state-of-the-art defence techniques against exploitation of memory error vulnerabilities like Address Space Layout Randomisation (ASLR) and Data Execution Prevention (DEP a.k.a  $W \oplus X$ ) can be circumvented under certain circumstances. We provide a new attack technique which even though addresses also issues specific to the *elf* executable format typically used by Unix-like operating systems, is of a more generic applicability, due to the fact that exploits specific characteristics belonging to the underlying hardware architecture, more specifically the Intel x86 ISA, i.e. the ability by the CPU of jumping in the middle of an instruction placed by the compiler, leading to the

execution of unintended instructions. In our experience on x86 code, intended instructions (placed intentionally by the compiler) aren't enough for mounting our proposed attack technique.

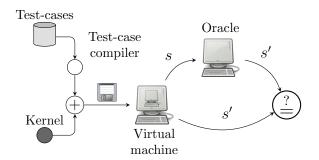

The first contribution consists of a fully automated testing methodology for CPU emulators, based on fuzzing [41]. The proposed methodology can be used to discover automatically configurations of the environment (i.e., state of the CPU registers and content of the memory) that cause different behaviours in the emulated and in the physical CPUs. To test an emulator we generate a large number of test-cases (i.e., configurations of the environment) and run these test-cases on both the emulated and the physical CPU. Then, we compare the configuration of the two environments at the end of the execution of each test-case; any difference is a symptom of an incorrect behaviour of the emulator. Given the unmanageable size of the test-case space, we adopt two strategies for generating test-cases: purely random test-case generation and hybrid algorithmic/random test-case generation. The latter guarantees that each instruction in the instruction set is tested at least in some selected execution contexts.

The work led to the implementation of this testing methodology in a proto-type for IA-32, code-named EmuFuzzer, and the testing of four state-of-the-art emulators: BOCHS[30], QEMU[4], Pin[34], and Valgrind[44]. Although Pin and Valgrind are dynamic instrumentation tools, their internal architecture resembles, in all details, the architecture of traditional emulators and therefore they can suffer the same problems. The work done with testing these emulators led to the discovery of several deviations in the behaviours of each of them, some of which represent serious defects that might prevent the proper execution of the emulated programs. Example are instructions that can freeze QEMU, instructions that are not supported by Valgrind and thus generate exceptions, and instructions that are executed by Pin and BOCHS but that cause exceptions on the physical CPU. The results obtained witness the difficulty of writing a fully featured and specification-compliant CPU emulator, but also prove the effectiveness and importance of this testing methodology.

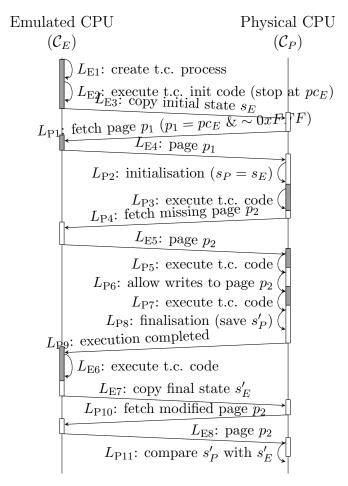

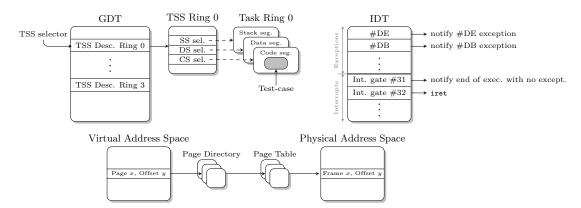

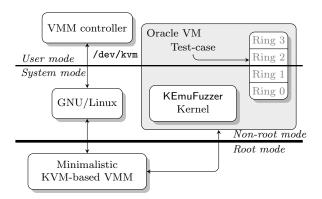

The second contribution of the dissertation consists of a testing methodology specific for system virtual machines. This represents an extension of the work done with EmuFuzzer which leads to the proposal of a much more powerful methodology independent from the technique used by virtual machines to execute guest code. More precisely, the testing technique used with EmuFuzzer is specific for testing CPU emulators (i.e., virtual machines based on CPU emulation) and limited to the testing of emulated user-mode code. The proposed technique can be used to test both user- and system-mode code and thus can also be applied to CPU virtualisers (i.e., virtual machines that rely on native code execution). The proposed methodology is based on the assumption that the CPU

of a perfect virtual machine behaves exactly as the physical CPU it simulates. Therefore, the intent of the testing is to verify whether such assumption holds. More precisely, this testing technique allows to discover sequences of instructions that, when executed, cause the CPUs of the virtual and of the physical machines to behave differently. The methodology is based on protocol-specific fuzzing [59] and differential analysis [39]. Fuzzing is used to generate automatically input states for the testing, and differential analysis to detect anomalous behaviours. Since the expected behaviour corresponds to what can be observed in the CPU of the physical machine, any difference between the behaviours of the physical and virtual machines is clearly anomalous, and consequently a symptom of a defect in the latter.

The second work led to the implementation of a prototype, code-named KEmu-Fuzzer, for testing virtual machines for the Intel x86 architecture. KEmuFuzzer has been used to test four popular system virtual machines: BOCHS [30], QEMU [4], VMWare [63], and VirtualBox [58]. The first two are based on emulation, while the others are based on direct native execution. In all the virtual machines has been found defects that led to the corruption of the state of the guest operating system or of its applications. The experimental evaluation testified the effectiveness of the proposed methodology and justified the significant effort made to extend it to system-mode code and CPU virtualisers.

The third contribution consists of a new approach to exploit stack-based buffer overflows in programs protected with both  $W \oplus X$  and ASLR and the related defence technique. The attack is an information leakage attack that exploits information about the random base address at which a library is loaded, available directly in the address space of the process, and is not avoidable. Contrarily to currently existing attack techniques consisting in mounting a brute-force attack, with the proposed technique an attacker can subvert the execution of a vulnerable program and perform a return-to-lib(c) with surgical precision, i.e., in a single shot. Furthermore, the technique works independently of the strength of randomisation (i.e., it works on 32 and on 64-bit architecture), and it is applicable to any position dependent executable. The impact of the proposed attack technique is not negligible, since the majority of executables found in modern UNIX distributions belong to this class.

The proposed protection technique is as effective as PIE (the only known protection scheme able to stop the proposed attack at the time of writing) at stopping our attack. Unlike PIE does not require recompilation of any executable, and introduces only negligible overhead. The proposed mitigation technique can be used to protect users of operating systems with ASLR and PIE, but that still have to adopt PIE on large scale (e.g., all GNU/Linux distributions). Moreover, our protection can be used by users of operating systems with ASLR, but

lacking PIE (e.g., OpenBSD), and by users of programs with no possibility of recompilation.

### 1.1 Summary of the contributions

To summarise the dissertation makes the following contributions:

- (ISSTA 2009) A testing methodology specific for CPU emulators, based on fuzzing consisting in forcing the emulator to execute specially crafted test-cases to verify whether the CPU is properly emulated or not. Improper behaviours of the emulator are detected by running the same test-case concurrently on the emulated and on the physical CPUs and by comparing the state of the two after the execution [36].

- (ISSTA 2010) A testing methodology specific for system virtual machines based on protocol-specific fuzzing and differential analysis consisting in forcing a virtual machine and the corresponding physical machine to execute specially crafted snippets of user- and system-mode code and comparing their behaviours [37].

- (ACSAC 2009) A new attack to bypass W⊕X and ASLR based on the leakage of sensitive information about the memory layout of a process and a new protection strategy against this technique which does not require recompilation introducing only a minimal overhead [51].

### 1.2 Organisation of the dissertation

The dissertation is organised as follows. Chapter 2 provides a brief introduction on some concepts used throughout the dissertation and compares the work presented in the dissertation with the work done by others. Chapter 3 describes a fully automated testing methodology implemented in the prototype code-named  $\mathsf{EmuFuzzer}$  capable of testing CPU emulators at the user-space level. Chapter 4 describes the extension of the work done with  $\mathsf{EmuFuzzer}$  for testing both privileged code and user-level code enabling us to test even System Virtual Machines. Chapter 5 describes an attack technique against widely adopted memory-error protections like  $\mathsf{ASLR}$  and  $\mathsf{W} \oplus \mathsf{X}$  and proposes also an alternative defence strategy against this kind of threats. The dissertation ends discussing possible improvements to the ideas presented and giving concluding remarks in Chapter 6.

### 2 Background and Related work

This chapter provides a brief introduction on the concepts used throughout the dissertation, briefly describing some basics on Intel x86 ISA, some challenges posed by Intel's architecture on emulation and a brief introduction to techniques used to exploit stack-based buffer overflows, focusing primarily on Intel x86 architecture. Since giving a complete overview of such concepts is beyond the scope of the dissertation, we redirect for this purpose the interested reader to the related literature.

### 2.1 Overview of Intel x86 ISA

Today, Intel x86 is the most widely adopted computer architecture. It is a complex CISC architecture, with a huge number of different instructions, of variable length, and a myriad of subtle and complex details. All that makes the development of an instruction decoder for this architecture a very tedious and error prone task.

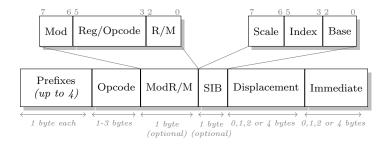

Figure 2.1 depicts the format of an Intel x86 instruction. An instruction is composed of different fields: it starts with up to 4 prefixes, followed by an opcode, an addressing specifier (i.e., ModR/M and SIB fields), a displacement and an immediate data field [24]. Opcodes are encoded with one, two, or three bytes, but three extra bits of the ModR/M field can be used to denote certain opcodes. In total, the instruction set is composed by more than 700 possible values of the opcode field. The ModR/M field is used in many instructions to specify non-

**Figure 2.1:** Intel x86 instruction format

implicit operands: the Mod and R/M sub-fields are used in combination to specify either registry operands or to encode addressing modes, while the Reg/Opcode sub-field can either specify a register number or, as mentioned before, additional bits of opcode information. The SIB byte is used with certain configurations of the ModR/M field, to specify base-plus-index or scale-plus-index addressing forms. The SIB field is in turn partitioned in three sub-fields: Scale, Index, and Base, specifying respectively the scale factor, the index register, and the base register. Finally, the optional addressing displacement and immediate operands are encoded in the Displacement and Immediate fields respectively. Since the encoding of the ModR/M and SIB bytes is not trivial at all, the Intel x86 specification provides tables describing the semantics of the 256 possible values each of these two bytes might assume.

### 2.1.1 Challenges on x86 emulation

In Computer Science, the term "emulator" is typically used to denote a software that simulates a hardware system [33]. The Church-Turing thesis implies that any operating environment can be emulated within any other. Consequently, any hardware system can be emulated via software. Despite the absence of any theoretical limitation that prevents the development of a correct and complete emulator, from the practical point of view, the development of such a software is very challenging. This is particularly true for *CPU emulators*, emulators that simulate a physical CPU.

Emulating an x86 CPU means facing the complexity of its instruction set which is already challenging by itself. It is easy to see that elementary decoding operations, such as determining the length of an instruction, require to decode the entire instruction format and to interpret the various fields correctly.

The advent of several instruction extensions (e.g., Multiple Math eXtension (MMX) and Streaming SIMD Extensions (SSE)) made the instruction decoding process even more complicated. As an example, consider the byte strings f3 ae and f3 0f e6, encoding respectively the instructions rep scasb and cvtdq2pd. The byte f3 is a prefix that is found in both instructions, but it serves two different purposes: it represents a rep prefix (to repeat the execution of an instruction) in the first case and a mandatory prefix for SSE instructions in the second case. Therefore, an instruction decoder has to consider that the prefix f3 has to be interpreted differently, according to the subsequent sequence of bytes. The decoder must treat the prefix as a rep only when it is followed by a sequence of bytes that encodes a string or I/O operation (e.g., scasb), and as a preamble for SSE instructions otherwise (e.g., cvtdq2pd).

Intel x86 instruction set has some redundancy w.r.t. the assembly represen-

tation of each instruction. Redundancy exists at the opcode level: consider for example the assembly code test byte [eax], 0x0. This instruction can be specified with two different opcodes f6/0 and f6/1, resulting in the encodings: f6 00 00 and f6 08 00. It is worth noting the latter representation is undocumented in Intel's manuals while Amd manuals report it.

We can find redundancy also in the memory addressing part: consider for example the assembly code mov [ecx],eax. Assemblers typically encode such instruction with the byte sequence 89 01, where 89 is the opcode of the mov instruction and 01 encodes both the memory reference [ecx] and the register eax. Playing with the ModR/M and SIB bytes, we can find alternative representations of the same instruction: (1) 89 04 21, (2) 89 04 61, (3) 89 04 a1 and (4) 89 04 e1.

Concluding, Intel x86 reference documentation sometimes lacks proper specifications for certain instructions, and states that others may have undefined effects in certain corner-cases. As an example, the effects on the OF flag belonging to the status register EFLAGS after the execution of the instruction shl dword [eax], cl (shift to the left the double-word pointed by eax by the amount specified in the cl register), when cl is different than 1, must be considered "undefined".

### 2.2 Software Testing

**Fuzz-testing** has been proposed by Miller et al. in 1990 [41], but it is still widely used for testing different types of applications. However, pure random fuzzing cannot guarantee a reasonable code coverage in case of applications that require a particular format of the input (e.g., a XML document or a well formed Java program). For this reason, several protocol-specific fuzzing techniques have been developed that leverage domain-specific knowledge [13, 25, 59]. Another approach consists of building constraints that describe what properties are required for the input to trigger execution of particular program paths, and then use a constraint solver to find inputs with these properties [10, 20, 53, 35].

Differential testing The idea of detecting software defects by comparing the behaviour of two or more software components for the same input is known as differential testing [39]. Differential testing has previously been used in a variety of contexts, including computer security [7], flash file systems [22], and grammar-driven functionality [29]. In [56] a technique based on differential analysis is used for testing Java Virtual Machines (JVMs). The idea is to feed the same test-case to different JVM implementations and to compare their output. Similarly to our test-case templates, they apply random mutators to perturb a meaningful input.

### 2.3 Emulators in malware analysis

CPU emulators are widely used in computer security for various purposes. One of the most common applications is malware analysis [3, 38]. Emulators allow fine-grained monitoring of the execution of a suspicious program and to infer high-level behaviours. Furthermore they allow to isolate execution and to easily checkpoint and restore the state of the environment. Malware authors, aware of the techniques used to analyse malware, aim at defeating those techniques for their software to survive longer. To defeat dynamic behavioural analysis based on emulators, they typically introduce routines able to detect if a program is run in an emulated or in a physical environment. As the average user targeted by the malware does not use emulators, the presence of an emulated environment likely indicates the program is being analysed. Thus, if the malicious program detects the presence of an emulator, it starts to behave innocuously such that the analysis does not detect any malicious behaviour. Several researchers have analysed state-of-the-art emulators to find unfaithful behaviours that could be used to write specific detection routines [45, 49, 52]. Unfortunately for them, their results were obtained through a manual scrutiny of the source code or rudimentary fuzzers, and thus the results are largely incomplete. The testing technique presented in the dissertation can be used to find automatically a large class of unfaithful behaviours a miscreant could use to detect the presence of an emulated CPU. These information could then be used to harden an emulator, to the point it satisfies the requirements for undetectability identified by Dinaburg et al. [15].

### 2.4 Buffer overflow

In high level languages like C, a buffer is declared as an array of data which can be of different types and different lengths. At the machine level, buffers loose these information and can be viewed roughly as a sequence of bytes with unspecified length. It is on a programmer's responsibility to keep track of each buffer length to avoid filling buffers with data beyond their capacity. When a program lacks this kind of checks, a buffer overflow condition can occur. Buffer overflows can be classified in many types, depending on where the declared buffer resides. We can have stack-based, heap-based and static data buffer overflows if the buffer resides respectively in the stack, heap or static data sections of a binary executable. Writing data beyond the buffer length leads to data corruption. The ability by an attacker of corrupting data such as code pointers can lead to arbitrary code execution if such code pointers are used afterwards.

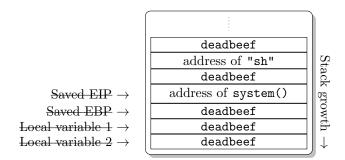

Stack-based buffer overflow is probably the most common and well-known buffer overflow vulnerability. Exploitation happens when a buffer stored in the stack has been filled beyond it's limits corrupting code pointers or data pointers like the saved return address of the calling function or the saved frame pointer. The first known techniques used for exploiting stack-based buffer overflow vulnerabilities involved the injection of executable code in the vulnerable buffer as long as carefully crafted data to overwrite the saved instruction pointer. The saved instruction pointer was typically filled with the address of the buffer itself, leading to execution of injected code, hence giving full control of the vulnerable program by the attacker. For such a technique to be successful, the attacker needs to know in advance the address of the overflown buffer (or at least an approximation) and the process must have the ability to execute code meant to be data by the application.

$\mathbf{W} \oplus \mathbf{X}$  is a defence strategy meant to prevent execution of injected code [61]. It is implemented marking each memory page meant to contain machine code as executable and read-only while marking each memory page meant to contain mutable data as read-write but not executable. Briefly no memory page is allowed to be both executable and writable at the same time. W $\oplus X$  was inspired by the belief: if a process were unable to execute attacker-supplied code, the attacker can no more force a vulnerable process to do arbitrary computations. Such belief was later proven to be false by techniques like return-to-libc and it's generalisation: return-oriented programming.

**Return-to-libc** is an attack technique developed to exploit vulnerabilities like stack-based buffer overflows and circumvent defence strategies like  $W \oplus X$  [14]. With  $W \oplus X$  the attacker can no longer inject it's own code. The usual exploit technique involving injection of the so-called shellcode (code meant to spawn a shell back to the attacker) can no longer be applied. However the attacker can still reliably corrupt code pointers to point to existing code. More precisely the attacker can execute useful functions belonging to the ubiquitous libc library, e.g. system to obtain a shell. Return-to-libc was believed to be limited as an attack technique for the inability by an attacker to execute arbitrary computations.

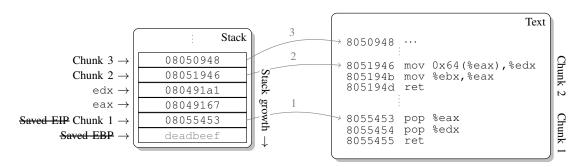

**Return oriented programming** is a generalisation of the return-to-libc technique. This technique was discovered by Shacham [54] and aims to prove the feasibility of arbitrary computation with no code injection at all. This technique consists of reusing small code snippets already present in the vulnerable process' address-space and ending with a ret instruction. Each code sequence

found accomplishes a single and simple task but glued together by means of carefully constructing a particular stack layout, they can be used to accomplish more complex tasks such as load/store operations, arithmetic operations or operations affecting the control flow such as direct or indirect jumps. Code sequences glued together to implement one of the aforementioned tasks are called "gadgets". The author has been able to identify enough gadgets sufficient to construct a Turing-complete machine, hence the possibility of doing arbitrary computations. Initially this technique was believed to be applicable only on CISC-based CPUs like x86 are, due to the ability to execute unaligned instructions, more precisely the ability of the CPU to jump in the middle of an instruction, leading to the execution of unwanted code. Later, Buchanan et al. [9] generalised the same technique to be applied on RISC architectures as well.

Address Space Layout Randomisation (ASLR) is a technique developed with the intention of hindering attacks like buffer overflow exploits [60]. For a successful exploitation of a buffer overflow, an attacker needs to know in advance some details on the layout of the vulnerable process. With the simplest stack-based buffer overflow technique the attacker needs to know the base address of the stack section, while for mounting a return-to-libc attack, he needs to know the base address of the libc library.

ASLR consists of randomising the base address of each section belonging to a process. In the presence of ASLR an attacker is no more able to know the base address of those sections since they are randomly chosen and they change at each execution of the vulnerable process. The only option for an attacker to successfully exploit these kind of vulnerabilities is by means of brute-force. However the most widely adopted incarnation of ASLR avoids randomising the base address of the code section belonging to the executable binaries, thus giving the attacker a chance to reliably jump to existing code.

Researchers have demonstrated that  $W \oplus X$  and ASLR can be defeated by patient attackers [55]. The state-of-the-art approach to exploit stack-based buffer overflows on systems protected with  $W \oplus X$  and ASLR involves mounting a return-to-lib(c) attack [14] repeatedly, in a brute-force fashion. Indeed, on 32-bit architectures (e.g., Intel x86) ASLR is weak because of low randomisation entropy. Hence, with a relatively small number of attempts an attacker can guess the base random address at which a certain library is loaded and then successfully mount a return-to-lib(c) attack. However, a brute-force attack can easily rise alarms (e.g., because of a large number of crashes) and automatic mechanisms can be used to impede the attacker [23].

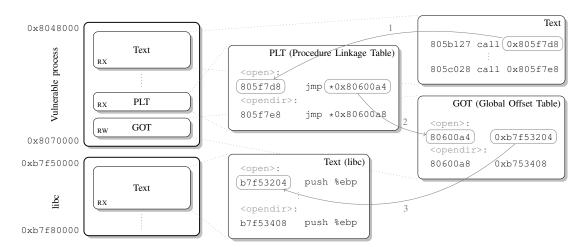

Position Independent Executables (PIE) RedHat extended the idea of position independent code to executables. Like shared objects, position independent executables (PIE) can be loaded at arbitrary memory locations [62]. In this dissertation, we present two variants of a new attack technique to exploit stack-based buffer overflow vulnerabilities. Both variants of the attack explained in chapter 5 exploit the lack of randomisation affecting some elf sections, e.g. .text, .plt and .got. None of the variants of our attack can be applied to position independent executables because, as for randomised libraries, the address of code chunks varies from one execution to another. Therefore, guessing the absolute address of a code chunk in an executable becomes as hard as reusing the code of a shared library. To further complicate the exploitation, position independent executables can also be used to construct self-randomising executables [6], executables that rearrange automatically, at each execution, the disposition of their functions.

**Code randomisation** Bhaktar *et al.* [5] proposed a randomisation scheme that uses binary rewriting to periodically re-obfuscate an executable, including the layout of the code section. The randomisation of the code section could prevent an attacker from using code chunks available in the executable. However, since re-obfuscation is periodic, a local attacker accessing the executable on disk can successfully mount both variants of our attack, within the time window in which the executable does not change.

GOT-related protections Xu et al. [65] designed a runtime system that randomises the location of the GOT and patches the PLT accordingly. This system essentially just adds a fake layer of security: the sensitive information we abuse in our proposed attack technique, (the content of the GOT) is stored at a random location, but the address of this location remains accessible in memory (in the PLT). Through our attack it is possible to dereference the PLT, discover the address of the GOT, and then overwrite or dereference any GOT entry. However, to perform GOT overwriting, the code chunks necessary for a dereference must be available in the executable. Recent versions of binutils include support for producing executables with a read-only GOT [19]. A similar protection could also be implemented at runtime, by adopting a system like the one proposed by Xu et al. Clearly such protection prevents our GOT overwriting attack, but it cannot mitigate the first variant of the attack. Unfortunately, despite the fact that this protection has been available in binutils for years, our experimental analysis demonstrated that this protection is not yet adopted by any distribution.

**N-Variant system** A completely different approach to detect memory corruptions is the N-Variant system [11]. The idea is to run n different instances of

the same program with diverse memory layouts, obtained using ASLR. Any successful attack will work only on one of the instances and will cause all the other instances to crash because the attack must be tailored to a particular process layout. This idea has been further extended in [8].

### 2.4.1 Notes on x86 unwanted code

Our proposed attack technique is based return-oriented programming [54]. However his technique does not take into account ASLR protected binaries and cannot be applied to the code section of a generic binary executable due to the lack of a sufficient number of usable code chunks, necessary to construct a Turing-complete machine. In our attack we look for code chunks in the code section of an elf binary. Due to the limited amount of code we can abuse w.r.t. code available in the libc library, more precisely due to the presence of very few code chunks ending with a ret instruction, we found to have a small chance of being successful in mounting our attack by looking for wanted code only (code intentionally placed by the compiler). The chance of success heavily increases if we take into account unwanted code too.

Unwanted code shows up by the ability of x86 CPUs to jump in the middle of an instruction, leading to a completely different computation.

| 8902   | mov | [edx],eax      |              |             |                    |

|--------|-----|----------------|--------------|-------------|--------------------|

| 83C42C | add | esp,byte +0x2c | 0283C42C89F0 | ${\tt add}$ | al,[ebx-0xf76d33c] |

| 89F0   | mov | eax,esi        | 5B           | pop         | ebx                |

| 5B     | pop | ebx            | 5E           | pop         | esi                |

| 5E     | pop | esi            | 5F           | pop         | edi                |

| 5F     | pop | edi            | 5D           | pop         | ebp                |

| 5D     | pop | ebp            | C3           | ret         |                    |

| C3     | ret |                |              |             |                    |

Figure 2.3: unwanted code

**Figure 2.2:** function epilogue

As an example, consider the code sequence in Figure 2.2. If we start disassembling in the middle of the first instruction, we obtain a different code sequence depicted in Figure 2.3. The former representing a typical function epilogue, the latter representing the unwanted code we abuse.

Despite the ability of Buchanan *et al.* [9] to apply return-oriented programming to RISC architectures like SPARC, which avoids the presence of unwanted code, we argue unwanted code is essential for our attack technique to be successful.

# 3 EmuFuzzer: a testing methodology for CPU emulators

This chapter presents a testing methodology specific for CPU emulators, based on fuzzing. The emulator is "stressed" with specially crafted test-cases, to verify whether the CPU is properly emulated or not. Improper behaviours of the emulator are detected by running the same test-case concurrently on the emulated and on the physical CPUs and by comparing the state of the two after the execution. Differences in the final state testify defects in the code of the emulator. We implemented this methodology in a prototype (code-named EmuFuzzer), analysed four state-of-the-art IA-32 emulators (QEMU, Valgrind, Pin and BOCHS), and found several defects in each of them, some of which can prevent the proper execution of programs.

### 3.1 Introduction

Defects in emulators may affect the execution of benign and malicious software. Emulators started to be used in the field of malware analysis for facilitating the analysis of suspicious software as they provide an isolated environment to safely execute potentially harmful programs. Dynamic malware analysis aims to spot harmful behaviours in software programs for identifying such threats and be able to react against them. Malicious software writers learnt to use techniques to fool malware analysis and evade detection. One of the evasion techniques they employ consists of detecting the presence of an emulator for not exposing their malicious behaviour to the potential analysis environment. To avoid this problem, emulators must be transparent w.r.t. the hardware they wish to emulate. Emulators are complex software, this is especially true if they have to emulate complex CISC architectures like x86. For their complexity they are also unlikely free of bugs.

Although several good tools and debugging techniques exist [42], developers of CPU emulators have no specific technique that can help them to verify whether their software emulate the CPU by following precisely the specification of the vendors.

| Instruction         | IA-32                           | QEMU                | Valgrind       | Pin               | BOCHS                    |

|---------------------|---------------------------------|---------------------|----------------|-------------------|--------------------------|

| lock fcos           | illegal instr.                  | lock prefix ignored | no diff.       | no diff.          | no diff.                 |

| int1                | trap                            | $no\ diff.$         | illegal instr. | no diff.          | general protection fault |

| fld1                | $\mathtt{fpuip} = \mathtt{eip}$ | fpuip = 0           | fpuip = 0      | FPU virtualised   | no diff.                 |

| add \$0x1,0x0(%eax) | 0x0(%eax) = 0xd0                | 0x0(%eax) = 0xcf    | no diff.       | $no\ diff.$       | no diff.                 |

| pop %fs             | %esp = 0xbfdbb108               | $no\ diff.$         | no diff.       | %esp = 0xbfdbb106 | no diff.                 |

| pop 0xffffffff      | %esp = 0xbffffe44               | no diff.            | no diff.       | no diff.          | %esp = 0xbffffe48        |

**Table 3.1:** Examples of instructions that behave differently when executed in the physical CPU and when executed in an emulated CPU (that emulates an IA-32 CPU). For each instruction, we report the behaviour of the physical CPU and the behaviour of the emulators (differences are highlighted).

Assuming that the physical CPU is correct by definition, the ideal CPU emulator mimics exactly the behaviour of the physical CPU it is emulating. On the contrary, the behaviour of an approximate emulator deviates, in certain situations, from the behaviour that one would have on the physical CPU. Some examples of the deviations we found in state-of-the-art emulators are reported in Table 3.1. As an example, let us consider the instruction add \$0x1,0x0(%eax), which adds the immediate 0x1 to the byte pointed by the register eax. Assuming that the original value of the byte is Oxcf, the execution of the instruction on the physical CPU, and on three of the tested emulators, the value of the byte is set to 0xd0. In QEMU, instead, the value is not updated correctly for a certain encoding of the instruction. Many other examples of problematic instructions are known already [17, 45, 48, 49, 52]. Our goal is to develop an automatic technique to discover deviations between the behaviour of the emulator and of the physical CPU it is emulating, caused by defects in the emulation code. We are not interested in deviations that lead only to internal differences in the state (e.g., differences in the state of CPU caches), because these differences are not visible to the programs running inside the emulated environment. Indeed, no instruction allows to observe such internal state and consequently the execution of emulated programs cannot be influenced. Apart from spotting semantic differences between instructions executed on the real CPU and by an emulated one, there are other ways to detect the presence of an emulator. Emulating a single instruction, tipically costs several CPU cycles. A malicious program willing to detect emulation could measure the time needed for a particular instruction sequence to execute. Detection could happen if the measured time is over some threshold. Such thresholds can be empirically obtained measuring time needed for direct CPU execution. Clearly, the work presented in the dissertation does not cover such collateral effects exposed by the emulation, being focused only on

$<sup>^1\</sup>mathrm{We}$  use IA-32 assembly and we adopt the AT&T syntax.

instruction semantics.

This chapter makes the following contributions:

- An automated testing methodology specific for CPU emulators, based on fuzzing and differential testing. We generate a large number of test-cases and run these test-cases on both the emulated and the physical CPU. We compare the configuration of the two environments looking for differences.

- A prototype implementation for IA-32 of the aforementioned testing technique code-named EmuFuzzer.

- Evaluation results of the prototype applied to four state-of-the-art emulators (BOCHS, QEMU, Pin, and Valgrind), allowed us to find bugs in all of them.

### 3.2 CPU Emulators

With the term CPU emulator we refer to a software that simulates the execution environment offered by a physical CPU. The execution environment consists of: an address space (the memory), general purposes registers, other classes of registers (e.g., FPU and management registers), and optionally I/O ports. The CPU emulator emulates a program by executing each instruction in the emulated execution environment. Instructions are typically executed using either interpretation or just-in-time translation. Emulated instructions mimic in every detail the behaviour of instructions executed directly by the physical CPU, with the exception that the former operates on the resources of the emulated execution environment, while the latter operates on the resources of the physical execution environment.

The execution environment can be properly emulated even if some internal components of the physical CPU are not considered (e.g., the instruction cache): as these components are used transparently by the physical CPU, no program can access them. Similarly, emulated execution environments can contain extra, but transparent, components not found in hardware execution environments (e.g., the cache used to store translated code).

### 3.2.1 Faithful CPU Emulation

Given a physical CPU  $C_P$ , we denote with  $C_E$  a software CPU emulator that emulates  $C_P$ . Our ideal goal is to automatically analyse  $C_E$  to tell whether it *faithfully* emulates  $C_P$ . In other words we would like to tell if  $C_E$  behaves equivalently to  $C_P$ ,

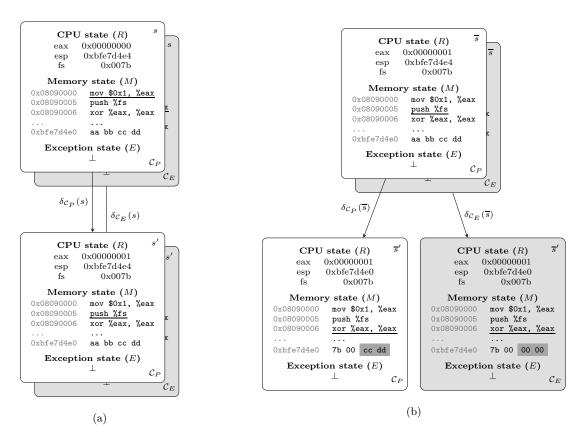

**Figure 3.1:** An example of our testing methodology with two different test-cases (s and  $\overline{s}$ ): (a) no deviation in the behaviour is observed, (b) the words at the top of the stack differ (highlighted in gray).

in the sense that any attempt to execute a valid (or invalid) instruction results in the same behaviour in both  $C_P$  and  $C_E$ .

To define how code is executed by a CPU we model the CPU with an abstract machine. A state of the abstract machine,  $s \in \mathcal{S}$ , consists of the program counter pc, the state of the CPU registers R, the state of the memory M, and the exception state E. For conciseness, we represent the state of the abstract machine with the tuple s = (pc, R, M, E). The CPU registers state R is a total mapping from CPU registers to their value. The memory state M is a total mapping  $M: A \to [0...255]$  of memory addresses to 1-byte memory values, where  $A = [0...2^N - 1]$  is the set of memory addresses, and N is the number of bits used by the CPU for memory addressing. The program counter  $pc \in A \cup \{\text{halt}\}$  can refer any memory address; halt is a special address used to denote the termination of the execution. We assume no distinction between code and data; thus any memory location can potentially be executed. Finally, the exception

state  $E \in \{\bot, illegal instruction, division by zero, general protection fault, ...\}$  denotes the exception that occurred during the execution of the last instruction; the special exception state  $\bot$  indicates that no exception occurred.

The abstract machine that models the CPU is a transition system  $(S, \delta)$ . The state-transition function  $\delta \colon S \to S$  maps a CPU state s = (pc, R, M, E) into a new state s' = (pc', R', M', E') by executing the current instruction at pc. The transition function  $\delta$  is defined as follows:

$$\delta(pc,R,M,E) \stackrel{\text{def}}{=} \begin{cases} (pc,R,M,E) & \text{if } pc = \text{halt} \lor E \neq \bot, \\ (pc,R,M,E') & \text{if an exception occurs,} \\ (pc',R',M',\bot) & \text{otherwise.} \end{cases}$$

If the program counter points to a valid instruction and the execution of that instruction does not raise any exception, then  $\delta(pc,R,M,E)=(pc',R',M',\perp)$ . The state of the registers R' and of the memory M' are updated according to the semantics of the executed instruction, the program counter pc' points to the next instruction, and  $E'=\perp$ . On the other side, if an exception occurs, then  $\delta(pc,R,M,E)=(pc,R,M,E')$ , with  $E'\neq\perp$ . An exception indicates that the instruction cannot be executed and, consequently, the program counter, the CPU registers, and the memory remain unvaried. When the last instruction is executed, the program counter is set to halt, and from that point on the state of the environment is not updated anymore. The same applies after an exception has occurred.

Having formalised how the CPU executes code, we can now define what it means for  $C_E$  to be a faithful emulator of  $C_P$ . Intuitively,  $C_E$  faithfully emulates  $C_P$  if the state-transition function  $\delta_{C_E}$  that models  $C_E$  is semantically equivalent to the function  $\delta_{C_P}$  that models  $C_P$ . That is, for each possible state  $s \in S$ ,  $\delta_{C_P}$  and  $\delta_{C_E}$  always transition into the same state. More formally,  $C_E$  faithfully emulates  $C_P$  iff:

$$\forall s \in \mathcal{S} : \delta_{\mathcal{C}_P}(s) = \delta_{\mathcal{C}_E}(s).$$

### 3.2.2 Fuzzing CPU Emulators

Obviously, proving that  $C_E$  faithfully emulates  $C_P$  is infeasible because of the unmanageable number of states that would have to be tested. For this reason, instead of trying to prove that  $C_E$  faithfully emulates  $C_P$ , we relax our goal and try to prove the opposite. That is, we search for an execution state  $\bar{s} \in \mathcal{S}$  that demonstrates that  $C_E$  does not faithfully emulates  $C_P$ . More formally,  $C_E$  unfaithfully emulates  $C_P$  iff:

$$\exists \bar{s} \in \mathcal{S} : \delta_{\mathcal{C}_{\mathcal{P}}}(\bar{s}) \neq \delta_{\mathcal{C}_{\mathcal{P}}}(\bar{s}).$$

Because we assume  $C_P$  to be correct, the existence of such a state testifies the existence of a defect in  $C_E$ .

Our approach to detect if  $C_E$  is not a faithful emulator of  $C_P$  is based on fuzzing. We generate a synthetic state (or test-case)  $s = (pc, R, M, \bot)$  and we set the state of both  $C_P$  and  $C_E$  to s. Then we execute the instruction pointed by pc in both  $C_P$  and  $C_E$ . At the end of the execution of the instruction, we compare the resulting state. If no difference is found, then  $\delta_{C_P}(s) = \delta_{C_E}(s)$  holds. On the other hand, a difference in the final states proves that  $\delta_{C_P}(s) \neq \delta_{C_E}(s)$  and therefore that  $C_E$  does not faithfully emulate  $C_P$ .

Figure 3.1 shows an example of our testing methodology in action. We run two different test-cases, namely s and  $\bar{s}$ . To ease the representation, in the figure we report only the meaningful state information (three registers and the content of few memory locations) and we represent the program counter by underlining the instruction it is pointing to. Furthermore, when the states of the two environments do not differ, we graphically overlap them. The first test-case s(Figure 3.1(a)) consists in executing the instruction mov \$0x1, %eax. We execute concurrently this test-case on  $\mathcal{C}_P$  and  $\mathcal{C}_E$ : we set the state of the two environments to s and we execute in both the instruction pointed by the program counter. We observe no difference in their final state. Therefore, we conclude that  $\delta_{\mathcal{C}_E}(s) = \delta_{\mathcal{C}_P}(s)$  and that, for the state s,  $\mathcal{C}_P$  is faithfully emulated by  $\mathcal{C}_E$ . The second test-case  $\bar{s}$  (Figure 3.1(b)) consists in executing the instruction push %fs, that saves the segment register fs on the stack. Although the register is 16 bits wide, the IA-32 specification dictates that, when operating in 32-bit mode, the CPU has to reserve 32 bits of the stack for the store. In the example we observe that  $\mathcal{C}_P$  leaves the upper 16 bits of the stack untouched, while  $\mathcal{C}_E$  overwrites them with zero (the different bytes are highlighted in the figure). The final state of the two environments differs because the content of their memory differs. Consequently, we have that, for  $\bar{s}$ ,  $\delta_{\mathcal{C}_P}(\bar{s}) \neq \delta_{\mathcal{C}_E}(\bar{s})$ . That proves that  $\mathcal{C}_E$  does not faithfully emulate  $\mathcal{C}_P$ . It is worth noting that this example reflects a real defect we have found in QEMU using our testing methodology.

### 3.3 EmuFuzzer

The development of the fuzzing-based approach just described requires two major efforts. First, as the number of states in which the environment has to be tested is prohibitively large, we have to focus our efforts on a small subset of states. Consequently, we have to carefully craft those states to avoid redundancy and to maximise the completeness of the testing. Second, the detection of deviations in the behaviours of the two environments requires to setup the two and to inspect their state at the end of the execution of each test-case. Thus, we need

to develop a mechanism to efficiently initialise and compare the state of the two environments. This section describes the details of our testing methodology.

Although the methodology we are proposing is architecture independent, our implementation, codenamed EmuFuzzer, is currently specific for IA-32. This choice is solely motivated by our limited hardware availability. Nevertheless, minor changes to the implementation would be sufficient to port it to different architectures. To ease the development, the current version of the prototype runs entirely in user-space and thus can only verify the correctness of the emulation of unprivileged instructions and whether privileged instructions are correctly prohibited. EmuFuzzer deals with two different types of emulators: process emulators that emulate a single process at a time (e.g., Valgrind, Pin, and QEMU), and whole-system emulators that emulate an entire system (e.g., BOCHS, Simics, and QEMU<sup>2</sup>).

### 3.3.1 Test-case Generation

In our testing methodology, the test-cases are merely the states of the environment under testing. For simplicity we consider a test-case as composed by data and code. If  $s = (pc, R, M, \bot)$  is the test case, the code consists in the bytes loaded in memory, representing the instruction (or the sequence of instructions) pointed by pc and that will be executed by the CPU. The data of the test-case are R and the remaining bytes of memory. To generate test-cases we adopt two strategies: (I) random test-case generation, where both data and code are random, and (II) CPU-assisted test-case generation, where data are random, while code is generated algorithmically, with the support of the physical and of the emulated CPUs. The advantage of using two different strategies is a better coverage of the test-case space.

Practically speaking, a test-case consists in a small assembly program, generated with one of the aforementioned techniques. Figure 3.2 shows a sample test-case (written in C for clarity). This program initialises the state of the environment, by loading the data of the test-case in memory (lines 5–9) and in the CPU (lines 11–13), and subsequently triggers the execution of the code of the test-case (lines 15–16). The program is compiled with special compiler flags to generate a tiny self-contained executable (i.e., that does not use any shared library).

<sup>&</sup>lt;sup>2</sup>QEMU supports both whole-system and process emulation.

```

1 void main() {

void *p;

char code[] = "code of the test-case";

// Initialise the memory with random data

for (p = 0x0; p < FILE_SIZE; p += FILE_SIZE) {</pre>

6

f = open(FILE_WITH_RANDOM_DATA, O_RDWR);

7

mmap(p, PAGE_SIZE, ..., MAP_FIXED, f, 0);

8

}

9

10

// Initialise the registers with random data

11

asm("mov RANDOM, %eax");

12

13

. . .

14

// Execute the code of the test-case (pc = code)

15

((void(*)()) code)();

16

17 }

```

**Figure 3.2:** Sample test-case (in C for clarity).

### **Random Test-case Generation**

In random test-case generation, both data and code of the test-case are generated randomly. The memory is initialised by mapping a file filled with random data. For simplicity, the same file is mapped multiple times at consecutive addresses until the entire user-portion of the address space is allocated. To avoid a useless waste of memory, the file is lazily mapped in memory, such that physical memory pages are allocated only if they are accessed. The CPU registers are also initialised with random values. As we work in user-space, we cannot allocate the entire address space because a part of it is reserved to the kernel. Therefore, to minimise page faults when registers are used to dereference memory locations, we make sure the value of general purpose registers fall around the middle of the allocated address space. Obviously, code generated with this approach might contain more than one instruction.

#### **CPU-assisted Test-case Generation**

A thorough testing of an emulator requires to verify that each possible instruction is emulated faithfully. Unfortunately, the pure random test-case generation approach presented earlier is very unlikely to cover the entire instruction set of

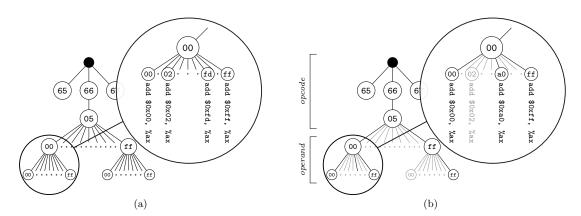

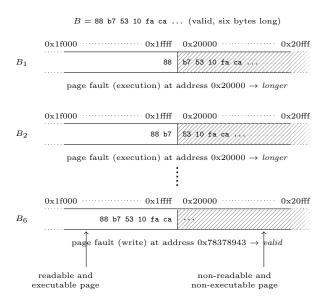

Figure 3.3: Example of CPU-assisted test-case generation for the opcode 6605 (mov imm16, %ax): (a) naïve and (b) optimised generation (paths in gray are not explored).

the architecture (the majority of CPU instructions require operands encoded using specific encoding and others have opcodes of multiple bytes). Ideally, we would have to enumerate and test all possible instances of instructions (i.e., combinations of opcodes and operands). Clearly this is not feasible. To narrow the problem space, we identify all supported instructions and then we test the emulator using only few peculiar instances of each instruction. That is, for each opcode we generate test-cases by combining the opcodes with some predefined operand values. As in random-test case generation, the data of the test-case are random.

Naïve Exploration of the Instruction Set Our algorithm for generating the code of a test-case leverages both the physical and the emulated CPUs, in order to identify byte sequences representing valid instructions. We call our algorithm CPU-assisted test-case generation. The algorithm enumerates the sequences of bytes and discards all the sequences that do not represent valid code. The CPU is the oracle that tells us if a sequence of bytes encodes a valid instruction or not: sequences that raise illegal instruction exceptions do not represent valid code. We run our algorithm on the physical and on the emulated CPUs and then we take the union of the two sets of valid instructions found. The sequences of bytes that cannot be executed on any of the CPUs are discarded because they do not represent interesting test-cases: we know in advance that the CPUs will behave equivalently (i.e., E' = illegal instruction). On the other hand, a sequence of bytes that can be executed on at least one of the two CPUs is considered interesting because it can lead to one of the following situations: (I) it represents a valid instruction for one CPU and an invalid instruction for the other; (II) it

encodes a valid instruction for both CPUs but, once executed, causes the CPUs to transition to two different states.

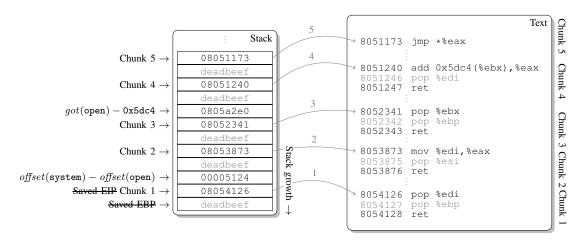

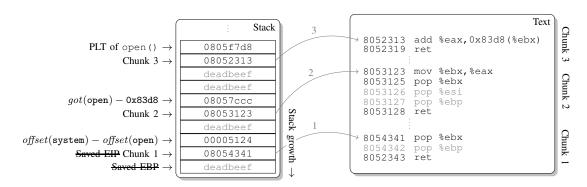

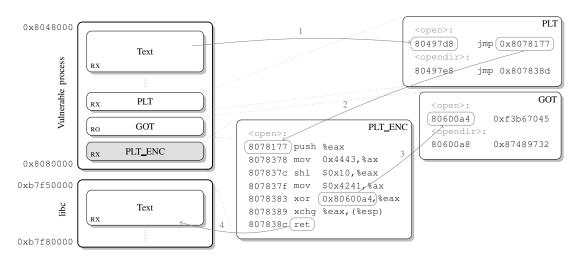

There are other possible approaches to generate the code of test-cases. For example, one can generate assembly instructions and then compile them with an assembler or use a disassembler to detect which sequences of bytes encode a legal instruction. However, limitations of the assembler or of the disassembler negatively impact on the completeness of the generated test-cases. Besides our approach, none of the ones just mentioned can guarantee no false-negative (i.e., that a sequence of bytes encoding a valid instruction is considered invalid).